# Using nanoscale thermocapillary flows to create arrays of purely semiconducting single-walled carbon nanotubes

Sung Hun Jin<sup>1†</sup>, Simon N. Dunham<sup>1†</sup>, Jizhou Song<sup>2</sup>, Xu Xie<sup>1</sup>, Ji-hun Kim<sup>1</sup>, Chaofeng Lu<sup>3,4</sup>, Ahmad Islam<sup>1</sup>, Frank Du<sup>1</sup>, Jaeseong Kim<sup>6</sup>, Johnny Felts<sup>5</sup>, Yuhang Li<sup>4</sup>, Feng Xiong<sup>6</sup>, Muhammad A. Wahab<sup>7</sup>, Monisha Menon<sup>1</sup>, Eugene Cho<sup>1</sup>, Kyle L. Grosse<sup>5</sup>, Dong Joon Lee<sup>6</sup>, Ha Uk Chung<sup>6</sup>, Eric Pop<sup>6</sup>, Muhammad A. Alam<sup>7</sup>, William P. King<sup>5</sup>, Yonggang Huang<sup>4</sup> and John A. Rogers<sup>1,5,6</sup>\*

Among the remarkable variety of semiconducting nanomaterials that have been discovered over the past two decades, single-walled carbon nanotubes remain uniquely well suited for applications in high-performance electronics, sensors and other technologies. The most advanced opportunities demand the ability to form perfectly aligned, horizontal arrays of purely semiconducting, chemically pristine carbon nanotubes. Here, we present strategies that offer this capability. Nanoscale thermocapillary flows in thin-film organic coatings followed by reactive ion etching serve as highly efficient means for selectively removing metallic carbon nanotubes from electronically heterogeneous aligned arrays grown on quartz substrates. The low temperatures and unusual physics associated with this process enable robust, scalable operation, with clear potential for practical use. We carry out detailed experimental and theoretical studies to reveal all of the essential attributes of the underlying thermophysical phenomena. We demonstrate use of the purified arrays in transistors that achieve mobilities exceeding 1,000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and on/off switching ratios of ~10,000 with current outputs in the milliamp range. Simple logic gates built using such devices represent the first steps toward integration into more complex circuits.

xploiting the exceptional electrical properties<sup>1,2</sup> of arrays of single-walled carbon nanotubes (SWNTs) in advanced applications<sup>3-9</sup> demands an ability to meet challenging requirements on degrees of alignment and purity in semiconducting behaviour. Direct, selective growth of purely semiconducting SWNTs (s-SWNTs) remains a topic of continuing study. Synthetic strategies that offer the greatest near-term potential fall into two categories: (i) purifying the SWNTs and then assembling them into arrays and (ii) assembling the SWNTs into arrays and then purifying them. The first has the advantage that it can build on recently developed wet chemical methods (ultracentrifugation<sup>10,11</sup>, chromatography<sup>12-14</sup> and others<sup>15,16</sup>) for purification. The disadvantages are that the resulting SWNTs are typically short ( $\sim 1 \mu m$ ), chemically modified and/or coated, and difficult to assemble into arrays with high degrees of alignment<sup>15,17–19</sup>. The second approach overcomes these limitations through the use of chemical vapour deposition techniques that, when used with quartz substrates, can yield nearly perfectly linear (>99.9% of SWNTs within  $0.01^{\circ}$  of perfect alignment), aligned arrays of long (100 µm and up to a few millimetres) and chemically pristine SWNTs<sup>3,20-23</sup>. The main difficulty is in removing the metallic SWNTs (m-SWNTs) from such arrays. Techniques based on optical<sup>24</sup>, electrical<sup>25</sup> or chemical<sup>26-28</sup> effects involve some combination of drawbacks, including incomplete removal of the m-SWNTs, partial removal and/or degradation of the s-SWNTs,

inability to operate on aligned arrays, and/or reliance on uncertain underlying mechanisms. Among these methods, electrical breakdown is noteworthy because it operates directly on the basis of relevant distinguishing characteristics in charge transport<sup>25</sup>. This scheme, however, has two critical disadvantages. First, the required high-power operation (~90  $\mu$ W  $\mu$ m<sup>-1</sup> for channel lengths >1  $\mu$ m, increasing as channel length decreases to values >1 mW  $\mu$ m<sup>-1</sup>)<sup>29-31</sup> leads to shifts in threshold voltage, avalanche effects<sup>32</sup>, band-toband tunnelling, failure in gate dielectrics, and significant heatsinking at the contacts<sup>29</sup>, all of which can prevent proper operation of the process. More significantly, breakdown only removes the m-SWNTs in isolated, narrow regions (~100 nm lengths) at locations that are not well controlled<sup>33</sup>. As a result, the vast majority of the m-SWNTs remain in the arrays<sup>34</sup>, thereby preventing generalized use in subsequently fabricated devices.

### Purification based on thermocapillary flow and etching

We introduce an approach for eliminating m-SWNTs in which thermocapillary effects in thin organic coatings allow their use as selective, self-aligned etch resists. Here, physical mass transport occurs via surface tension gradients generated through spatial variations in temperature<sup>35</sup> associated with selective heating in the m-SWNTs. We illustrate these concepts through the complete physical removal of all m-SWNTs from linear, horizontally aligned arrays

<sup>&</sup>lt;sup>1</sup>Departments of Materials Science and Engineering, Frederick Seitz Materials Research Laboratory, University of Illinois at Urbana-Champaign, Urbana, Illinois 61801, USA, <sup>2</sup>Department of Mechanical and Aerospace Engineering, University of Miami, Coral Gables, Florida 33146, USA, <sup>3</sup>Department of Civil Engineering and Soft Matter Research Center, Zhejiang University, Hangzhou 310058, China, <sup>4</sup>Department of Civil and Environmental Engineering and Department of Mechanical Engineering, Northwestern University, Evanston, Illinois 60208, USA, <sup>5</sup>Department of Mechanical Science and Engineering, University of Illinois at Urbana-Champaign, Urbana, Illinois 61801, USA, <sup>6</sup>Department of Electrical Engineering, University of Illinois at Urbana-Champaign, Urbana, Illinois 61801, USA, <sup>6</sup>Department of Electrical Engineering, University of Illinois at Urbana-Champaign, Urbana, Illinois 61801, USA, <sup>6</sup>Department of Electrical Engineering, University of Illinois at Urbana-Champaign, Urbana, Illinois 61801, USA, <sup>6</sup>Department of Electrical Engineering, Urbana, Illinois 61801, USA, <sup>6</sup>Department of Electrical Engineering, Urbana, Urbana, Illinois 61801, USA, <sup>7</sup>School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907, USA, <sup>†</sup>These authors contributed equally to this work. \*e-mail: jrogers@uiuc.edu

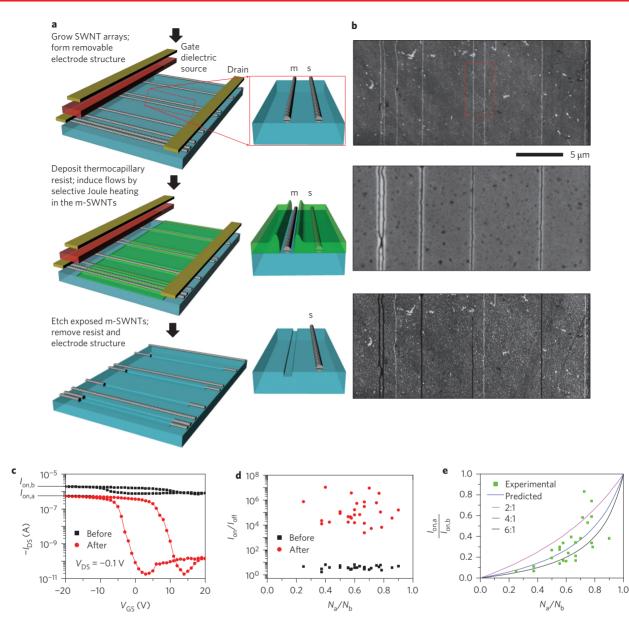

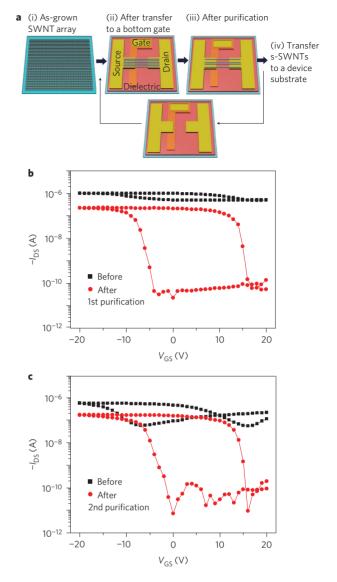

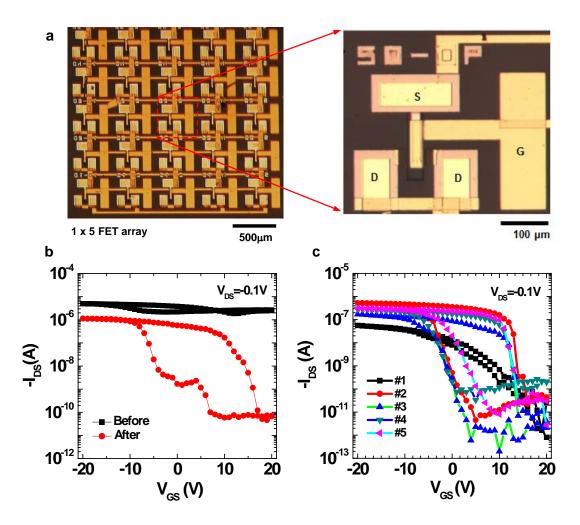

**Figure 1** | **Process for exploiting thermocapillary effects in the purification of arrays of SWNTs. a,b**, Schematic illustration (**a**) and corresponding AFM images (**b**) of various stages of the process applied to an array of five m-SWNTs and three s-SWNTs. Uniform thermal evaporation forms a thin, amorphous organic coating that functions as a thermocapillary resist. A series of processing steps defines a collection of electrodes and dielectric layers for selective injection of current into the m-SWNTs. The Joule heating that results from this process induces thermal gradients that drive flow of thermocapillary resist away from the m-SWNT, to form open trenches with widths, measured near the substrate, of ~100 nm. Reactive ion etching physically eliminates the m-SWNT exposed in this fashion, while leaving the coated s-SWNTs unaltered. Removing the thermocapillary resist and electrode structures completes the process, to yield arrays comprising only s-SWNTs. **c**, Typical transfer characteristics for a transistor built with an array of SWNTs in a partial gate geometry, evaluated before and after purification. Quantities  $I_{on,b}$  and  $I_{on,a}$  correspond to currents measured in the on states before and after purification, respectively. Here, the on/off ratio improves by a factor of  $2 \times 10^4$ , while  $I_{on,a}/I_{on,b}$  remains relatively large (~0.25). **d**, Ratios between currents in the on and off states before purification ( $I_{on,b}$  and  $I_{offa}$ , respectively) as a function of the ratio of the number of SWNTs after purification ( $N_a$ ) to the number of SWNTs. **e**, Ratio of  $I_{on,a}$  to  $I_{on,b}$  as a function of the entire set of devices with  $N_b > 7$ . The results are consistent with modelling (lines) that assumes complete retention of s-SWNTs through the purification process, expected relative populations of s-SWNTs and m-SWNTs in the arrays, and ratios of conductivities of m-SWNTs and s-SWNTs (in their on state) that lie in an experimentally expected range.

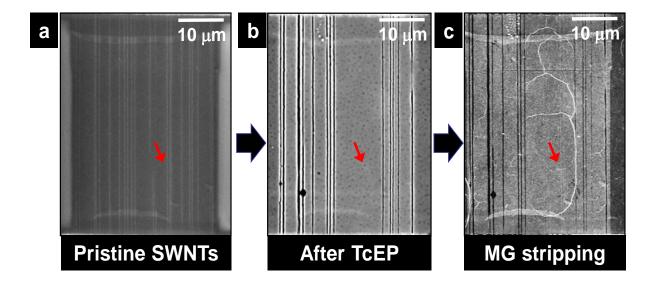

that contain both m-SWNTs and s-SWNTs, without any measurable adverse effects on the latter. Figure 1a,b presents schematic illustrations and corresponding atomic force microscope (AFM) images of the process applied to a heterogeneous collection of SWNTs grown on quartz. Arrays formed in this fashion consist of individual, isolated SWNTs, with very few multiwalled nanotubes or bundles of SWNTs, but with a distribution of diameters between ~0.6 nm and ~2.0 nm and a range of chiralities<sup>23,31</sup>. The key element in the purification process is an ultrathin (~25 nm) amorphous layer of a small-molecule organic species, in this example  $\alpha$ , $\alpha$ , $\alpha'$ -tris(4-hydroxyphenyl)-1-ethyl-4-isopropylben-zene<sup>36</sup>, deposited uniformly over the arrays of SWNTs by thermal evaporation. We refer to this film (Supplementary Fig. S2) as a thermocapillary resist. As well as having favourable thermophysical properties, this particular material is well suited for the present purposes because it combines hydroxyl and phenyl moieties to

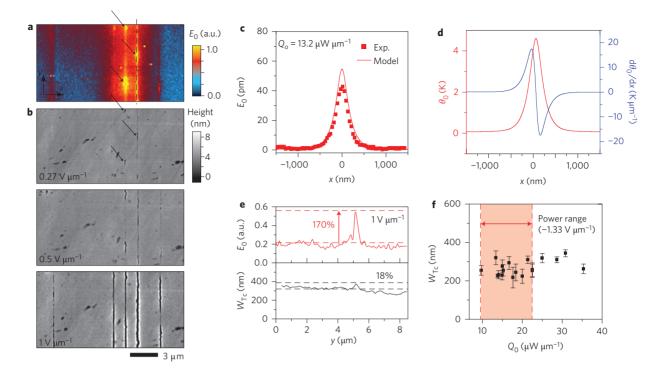

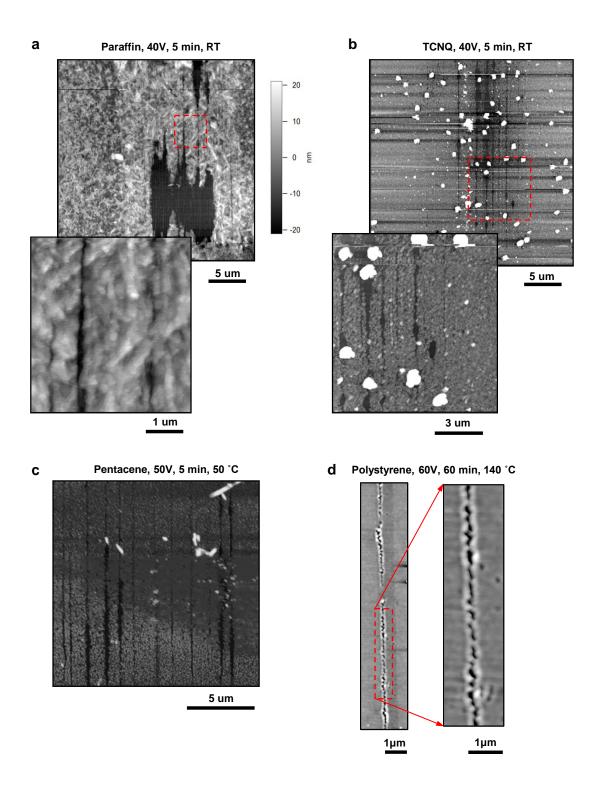

Figure 2 | Thermal origins and power scaling in behaviour of the thermocapillary resists. a, Scanning Joule expansion microscope image of an array of SWNTs in an operating, two-terminal device on quartz. The electrodes (separation of ~30 µm) are above and below the image, out of the field of view. Coordinates x and y lie perpendicular and parallel to the direction of alignment of the SWNTs, respectively. **b**, Topographical images of the device in **a**, coated with a thin (~25 nm) layer of thermocapillary resist, collected after operation at bias conditions of 0.27 V  $\mu$ m<sup>-1</sup> (top), 0.5 V  $\mu$ m<sup>-1</sup> (middle) and 1.0 V  $\mu$ m<sup>-1</sup> (bottom). Comparison of these images with those collected by scanning Joule expansion microscopy reveals a clear correlation between a.c. expansion  $(E_{0}, \text{ and therefore temperature})$  and the formation of trenches in the thermocapillary resist (d.c. heating). **c**, Thermal expansion  $E_{0}$  (a.c.) induced by Joule heating in an individual SWNT with input power density  $Q_0 \approx 13 \,\mu\text{W} \,\mu\text{m}^{-1}$  (peak to peak), measured by scanning Joule expansion microscopy (symbols) as a function of position x, where x = 0 is the location of the SWNT on a SiO<sub>2</sub>/Si substrate. Results of thermomechanical modelling are shown as a line. **d**, Computed a.c. temperature rise  $\theta_0$  and thermal gradients  $d\theta_0/dx$  at the surface of the thermocapillary resist using experimentally validated models, for the case of the SWNT in c. The results indicate small increases in temperature for levels of Joule heating that induce trenches in the thermocapillary resist (~3-10  $\mu$ W  $\mu$ m<sup>-1</sup>). **e**, Top graph: a.c. thermal expansion (arbitrary units) measured by scanning Joule expansion microscope along the length y of the fourth SWNT from the left in the array that appears in a and b. Bottom graph: width of the corresponding trench that appears in the thermocapillary resist  $(W_{T_r}$  measured at the top of the film) for an applied bias of ~1 V  $\mu$ m<sup>-1</sup>. The results show variations in  $W_{T_c}$  that are nearly ten times smaller than those in expansion (and therefore temperature).  $\mathbf{f}$ , Measurements of the average  $W_{T_{C}}$  as a function of  $Q_{0}$ . The results reveal no systematic dependence on  $Q_{0}$  over this range. The highlighted region corresponds to the values of Qo associated with optimized conditions for the purification process. Error bars indicate the standard deviation of the range of measured widths.

facilitate the formation of uniform, continuous coatings on the surfaces of both the quartz and the SWNTs. This behaviour is critical for its role as an effective etch resist with extremely small thicknesses.

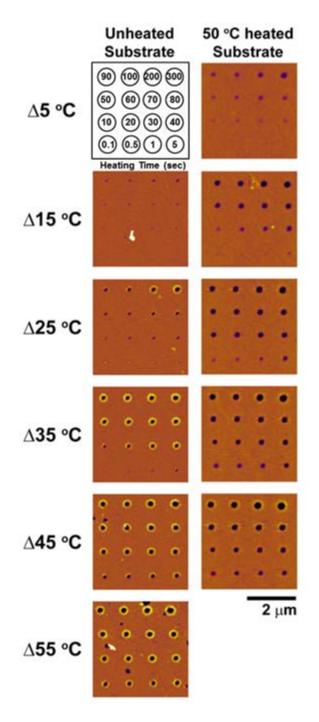

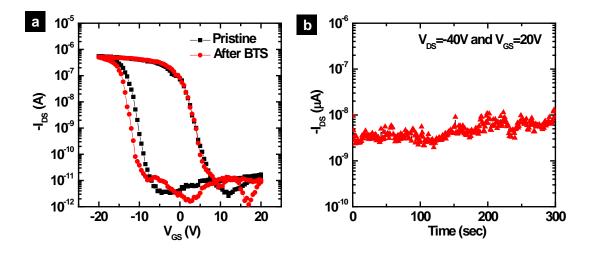

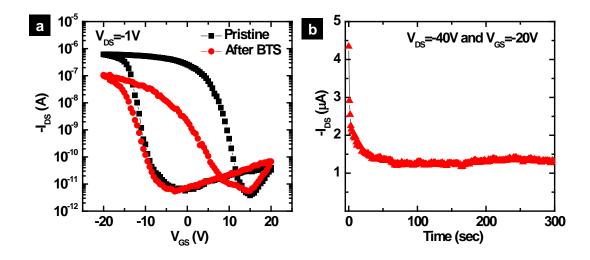

Metal and dielectric layers patterned at the edges of an area of interest enable current injection primarily into only the m-SWNTs, due to controlled electrostatically induced increases in the heights and widths of the Schottky barriers at the source ends of the s-SWNTs (Fig. 1a; Supplementary Figs S4, S25-S27). These layers represent removable, transistor structures in which the gates extend beyond the source electrodes by a distance that is small  $(\sim 5 \,\mu m)$  compared to the separation between the source and drain ( $\sim$ 30 µm). Applying a positive voltage to the gate ( $\sim$ 20 V) and a negative voltage to the drain (-40 V to -50 V), while holding the source at electrical ground, leads to selective Joule heating only in the m-SWNTs as a result of approximately unipolar p-type behaviour in the s-SWNTs. (Supplementary Figs S21 and S22 illustrate the good stability in the current outputs.) This set of bias conditions produces small increases in temperature only in the vicinity of the m-SWNTs. The large thermal gradients associated with nanoscale localization of these heat sources in turn drive mass transport in the thermocapillary resist. In typical experiments (fields of  $V_{\rm DS}/L_{\rm ch} \approx 1.33 - 1.66 \text{ V} \,\mu\text{m}^{-1}$  along the SWNTs for 5 min, with substrate heating to 60 °C in vacuum, where  $V_{\rm DS}$  is the drain–source bias and  $L_{\rm ch}$  is the distance between the electrodes), the resulting flows yield trenches centred at the m-SWNTs and extending throughout the thickness of the thermocapillary resist (Fig. 1b). Although most experiments were performed in vacuum  $(1 \times 10^{-4} \text{ torr})$ , inert environments can also be used (for example, dry nitrogen or argon). Excluding oxygen can help to prevent electrical breakdown in extreme cases of hot spots along the lengths of the SWNTs with localized defects. Reactive ion etching (RIE, O<sub>2</sub>/CF<sub>4</sub>) after thermocapillary flow eliminates only the m-SWNTs. Removing the residual thermocapillary resist and the metal/dielectric structures leaves a purified array of s-SWNTs, in a configuration well suited for planar integration into diverse classes of devices and sensors.

### Efficiency of the purification process

A key feature of this process is its exceptional efficiency in removing the m-SWNTs completely and exclusively. Such operation is important because most envisioned applications of s-SWNTs in electronics require purity at the level of 99.99% or better. For present purposes, we define a SWNT as metallic if the ratio between the on  $(I_{on})$  and off  $(I_{off})$  currents (that is, the on/off ratio) in a welldesigned transistor structure that incorporates this SWNT is less

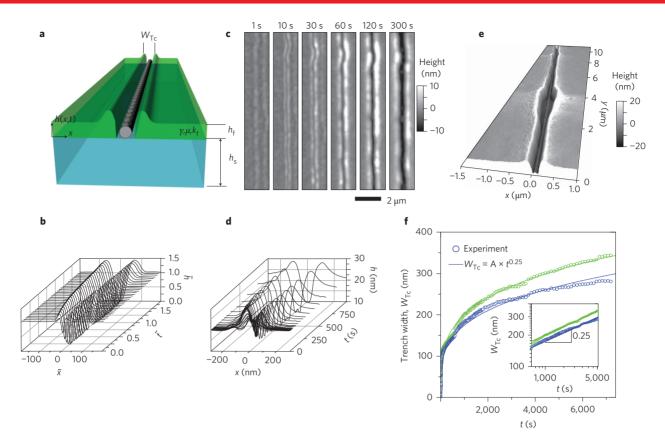

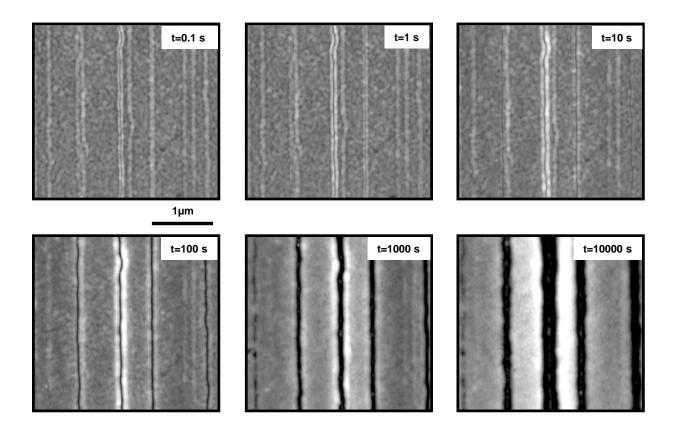

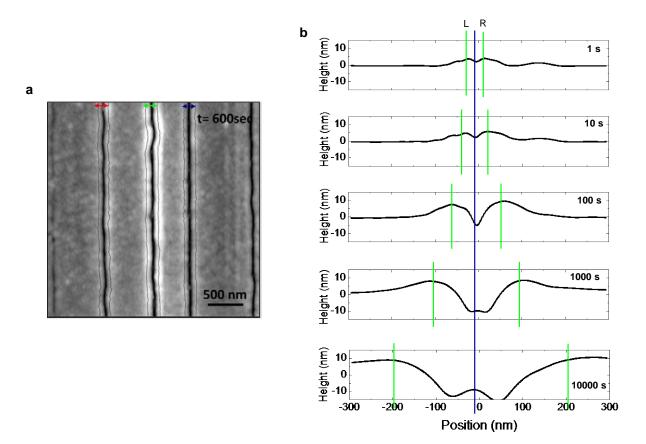

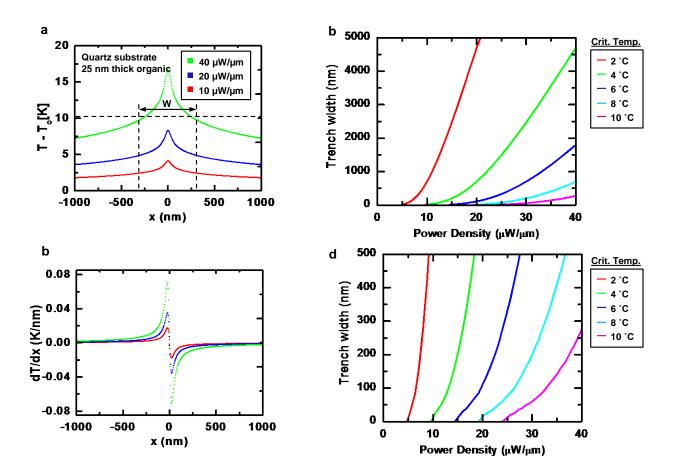

**Figure 3** | Nanoscale thermocapillary flows in thermocapillary resists induced by Joule heating in SWNTs. a, Schematic illustration of the geometry of the system, with key parameters defined. The SWNT, thermocapillary resist and substrate are grey, green and blue, respectively. **b**, Theoretically calculated normalized surface profiles of the thermocapillary resist,  $\bar{h}$ , as a function of normalized distance  $\bar{x}$  and time  $\bar{t}$ , showing the evolution of the trench geometry with thermocapillary flow. The simulations used polystyrene because relevant materials parameters were available in the literature. **c**, AFM images of a SWNT coated with thermocapillary resist (~25 nm) after Joule heating (0.66 V  $\mu$ m<sup>-1</sup>) for 1, 10, 30, 60, 120 and 300 s, induced by current injection at electrodes that lie outside of the field of view. Thermocapillary flow creates a trench that aligns to the SWNT and grows in width over time. **d**, Averaged cross-sectional profiles extracted from measurements like those shown in **c**. The results compare favourably to the modelling in **b**. **e**, AFM image, rendered in a three-dimensional perspective view collected at a duration of 1,800 s. The width in this case is sufficiently large that AFM measurements clearly reveal that thermocapillary flow completely and cleanly exposes the SWNT. **f**, Widths of trenches measured by AFM from the ridges that form at the top surface ( $W_{Tc}$ ), shown as a function of time of Joule heating for two different SWNTs, with a field of 0.66 V  $\mu$ m<sup>-1</sup>. Both model and experiment show a power-law time dependence with an exponent of 0.25.

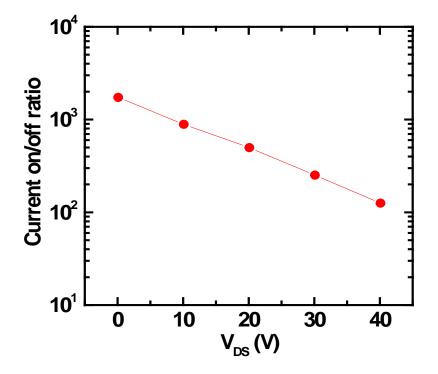

than  $\sim$ 100, and define it as semiconducting if this ratio is greater than  $\sim$ 100. This definition places SWNTs that are sometimes referred to as quasi-metallic into the m-SWNT classification. (In all cases, for populations of SWNTs grown on quartz, we observe a clear distinction between the behaviour of m-SWNTs and s-SWNTs defined in this way; in particular, of the hundreds of SWNTs studied here and elsewhere, none exhibit on/off ratios between ~50 and ~1,000.37) Detailed electrical characterization (that is,  $I_{on}$  and  $I_{off}$  before and after purification) and assessment of statistics (that is, total numbers of SWNTs before and after) performed on significant numbers of devices (35 devices, each with an active area of  $\sim 30 \times 30 \ \mu\text{m}^2$  to enable full visualization by AFM; 377 SWNTs in total) provide quantitative insights into the effectiveness of the process. Figure 1c shows a representative transfer characteristic for a device before and after purification, measured in air using the same metal/dielectric structures that enable selective Joule heating. The results illustrate a dramatic reduction in  $I_{\text{off}}$ (from 0.7  $\mu$ A to 2 × 10<sup>-5</sup>  $\mu$ A), thereby improving the on/off ratio from 2.7 to a value of  $3 \times 10^4$ . All devices demonstrated on/off ratios of less than 10 (median = 3.7) before and greater than  $2 \times 10^3$  (median =  $6.6 \times 10^4$ ) after purification, independent of the number of SWNTs removed (Fig. 1d). The relatively small numbers (<30) of SWNTs in each device used to examine the statistics led to the conclusion that the observed on/off ratios correspond to complete removal (that is, 100%) of the m-SWNTs.

Other results suggest that the process also preserves most or all of the s-SWNTs. First, of the 377 SWNTs present initially, 63% (that is, 238 SWNTs) remain after purification. This outcome is consistent with the expected percentage ( $\sim$ 66%) of s-SWNTs in collections of SWNTs grown by chemical vapour deposition<sup>3,38</sup>. Second, among the 28 devices where SWNT type could be determined from electrical behaviours measured before and after purification (that is, those that incorporate  $\leq 2$  SWNTs), all the m-SWNTs and none of the s-SWNTs show trenches (for optimized conditions; see Supplementary Fig. S1). Third, reductions in  $I_{on}$  induced by purification are modest; for the device shown in Fig. 1c the ratio of  $I_{\rm on}$ after the process to its value before is  $I_{\rm on,a}/I_{\rm on,b} \approx 25\%$ . The weighted average from all of the devices is  $I_{\rm on,a}/I_{\rm on,b} \approx 30\%$ . These results can be interpreted by examining the dependence of  $I_{on,a}/I_{on,b}$  on the percentage of SWNTs removed (Fig. 1e). The trends are consistent with models that assume 100% preservation of s-SWNTs, expected populations of s-SWNTs and m-SWNTs, and ratios of conductances of m-SWNTs to s-SWNTs (in their on state) that are within an experimentally observed range of 6:1 and 2:1 (Supplementary Fig. S3). Collectively, then, all observations suggest highly selective and efficient purification, in which all m-SWNTs are eliminated, and most

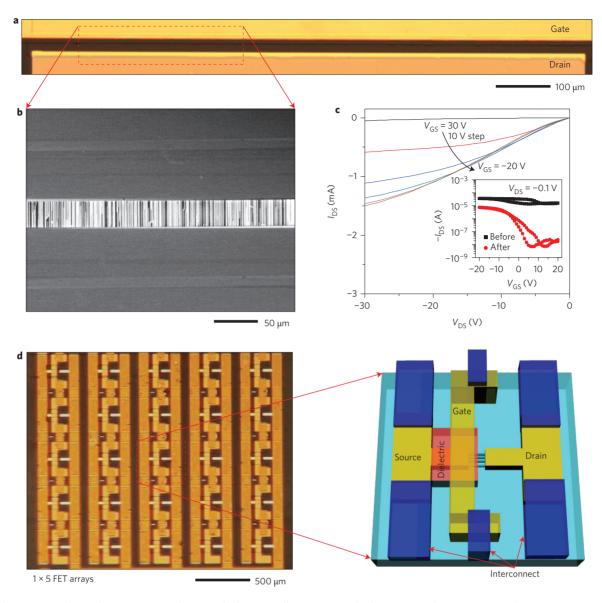

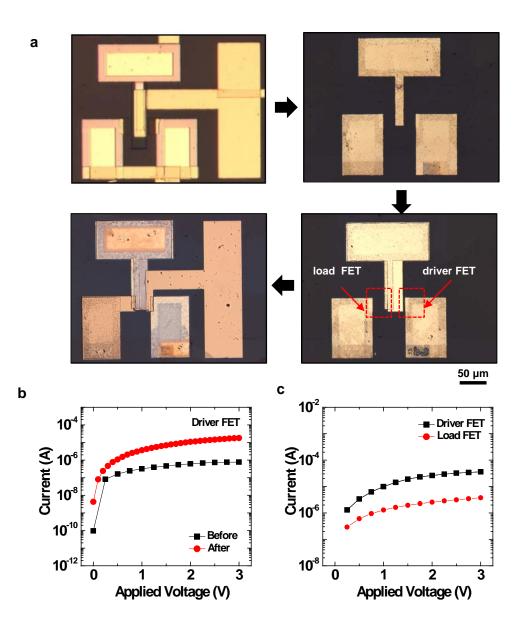

**Figure 4 | Description of two alternative approaches to scale thermocapillary separation for large-area applications. a**, Optical microscope image of a set of electrodes for thermocapillary purification of an array of many hundreds of SWNTs. **b**, Scanning electron microscope image of a small region of the structure shown in **a**. **c**, Transfer characteristics before and after removal of m-SWNTs from the region between the electrodes shown in **a**. The results indicate outcomes consistent with observations from small-scale demonstrations, that is, high on/off ratios of  $\sim 1 \times 10^3$  and modest reductions in on current  $(I_{on,a}/I_{on,b} \approx 20\%)$ . **d**, Optical micrograph and schematic illustration of an alternative mode for scaled implementation. An interconnected array of 25 sets of electrodes allows purification over a collection of small regions, in a parallel fashion. Associated transfer curves are similar to those shown in **c**.

or all s-SWNTs are preserved without degradation. Rigorous electrostatic analysis indicates mobilities of  $\sim$ 1,000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for the s-SWNTs (see Supplementary Fig. S18 for details), similar to values previously reported from unpurified arrays<sup>3,4</sup>.

#### Studies of nanoscale thermocapillary flow

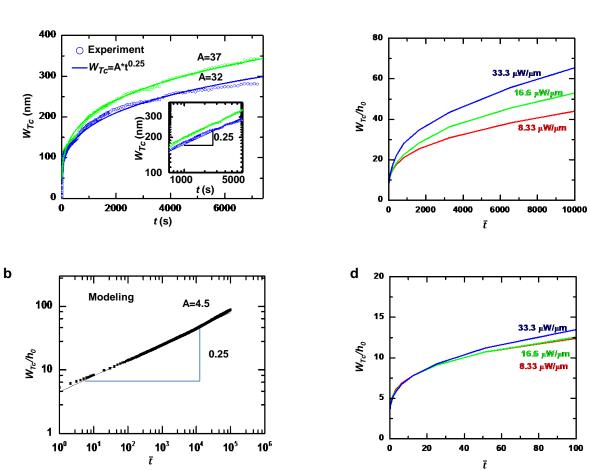

Detailed experimental and theoretical studies reveal quantitative aspects of heat transport and thermocapillary flow. We start by examining the distributions of temperature generated during Joule heating and their role in the behaviour of the thermocapillary resist. Figure 2a presents a scanning Joule expansion microscope<sup>39,40</sup> image of the thermal expansion that results from Joule heating in an array of SWNTs, at a drain–source bias condition of  $V(t) = V_{\rm DS} \cos(2\pi f t)$ , with  $V_{\rm DS} = 5$  V and f = 386 kHz. Here, Joule heating with a power density of  $Q(t) = Q_0[1 + \cos(4\pi f t)]/2$  yields a.c. thermal expansion at a frequency of 2f, according to  $E(t) = [E_1 + E_0 \cos(4\pi f t)]/2$ . Components  $E_1$  and  $E_0$  correspond

to d.c. and a.c. thermal expansion, respectively. The image signal corresponds to the peak-to-peak value of the a.c. expansion,  $E_0$ . Figure 2b shows topographical images of the same array coated with thermocapillary resist after application of several increasing values of  $V_{\rm DS}$  (direct current for 5 min; substrate temperature 60 °C). A key observation is that the distributions in expansion, and therefore temperature (Fig. 2a), correspond directly to the geometries of trenches that appear in the thermocapillary resist (Fig. 2b). For instance, trenches progressively form with increasing  $V_{\rm DS}$  in an order consistent with the temperatures revealed by the scanning Joule expansion microscopy; trenches at the second and fifth SWNT from the right appear first and last, respectively. Related effects can be observed along an individual SWNT, where trenches nucleate in areas of enhanced temperature ('hot spots'; arrows in Fig. 2a and the top frame of Fig. 2b). These indications establish a clear, although qualitative, connection between temperature and operation of the thermocapillary resist.

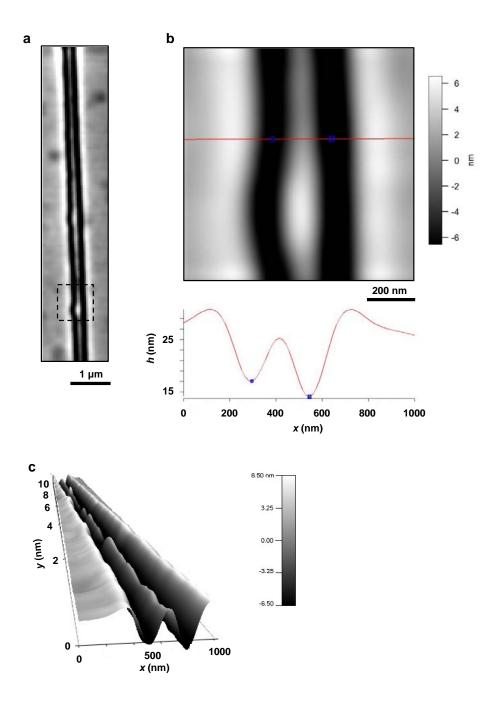

The first step towards quantitative understanding is an experimentally validated model for nanoscale heat flow in this system. Raw data from measurements by scanning Joule expansion microscopy indicate relative temperature increases but not their absolute values. Figure 2c shows a representative cross-sectional profile of  $E_0$  for the case of a SWNT of length  $\sim$ 3.5 µm (the corresponding scanning Joule expansion microscopy image is shown in Supplementary Fig. S5). The power density per unit length is Q(t), with  $Q_0$  estimated to be ~13  $\mu$ W  $\mu$ m<sup>-1</sup> based on the total input power into the device, which includes three SWNTs on an SiO<sub>2</sub>/Si substrate. Analytical models of temperature distributions that treat the SWNT as a line heat source with length L and input power density Q(t) can be developed (Supplementary Fig. S6). Boundary conditions involve continuous temperature and heat flow at all material interfaces except those with the SWNT, negligible heat flow at the top surface, and a constant temperature at the base of the substrate. At the SWNT interface, discontinuous heat flow Q(t) is assumed as a means to introduce the source of Joule heating. The results, together with materials constants taken from the literature (Supplementary Table S1) and analytical treatments of the resulting thermal expansion, yield expansion profiles that have both peak magnitudes ( $E_0 \approx 50$  pm) and spatial distributions (characteristic widths  $\sim$ 340 nm) consistent with the scanning Joule expansion microscopy results ( $\sim$ 40 pm and  $\sim$ 320 nm, respectively) when  $Q_0 \approx 13 \ \mu\text{W} \ \mu\text{m}^{-1}$ , the estimated experimental value. Figure 2d shows the associated a.c. temperature increases  $\theta_0$ and thermal gradients  $d\theta_0/dx$ , where  $\theta(t) = [\theta_1 + \theta_0 \cos(4\pi f t)]/2$ . When applied to the case of d.c. heating (f = 0 Hz), and quartz substrates, the same analytical model yields an expression for the rise in temperature of the surface of the thermocapillary resist,  $\theta = T - T_{\infty}$ , where  $T_{\infty}$  defines the temperature of the background,

$$\theta(x, y) = \frac{1}{2k_{s}\pi} \int_{-L/2}^{L/2} \mathrm{d}\eta \int_{0}^{\infty} \frac{Q_{0}J_{0}\left(\xi\sqrt{(\eta - y)^{2} + x^{2}}\right)}{\cosh(\xi h_{f}) + \frac{k_{f}}{k_{s}}\sinh(\xi h_{f})} \mathrm{d}\xi \quad (1)$$

Here,  $k_{\rm s}$  and  $k_{\rm f}$  are the thermal conductivities of the thermocapillary resist and quartz substrate, respectively, and  $h_{\rm f}$  is the thickness of the resist. This solution, which is also consistent with three-dimensional finite-element analysis (ABAQUS), suggests small increases in temperature at the SWNTs (~2–5 °C) for the power densities needed to achieve trenches. The flows arise from large associated gradients in temperature (~20 °C µm<sup>-1</sup>) (Supplementary Fig. S6). Studies of flow induced with heated tips in an AFM verify the low-temperature operation (Supplementary Fig. S10).

The characteristics of this flow provide several attractive features for present purposes, one of which is immediately evident from inspection of Fig. 2a,b. At large  $V_{\rm DS}$  ( $V_{\rm DS}/L_{\rm ch} > 1$  V  $\mu$ m<sup>-1</sup>), the trenches associated with SWNTs that have pronounced hot spots exhibit uniform widths. Likewise, SWNTs that show vastly different temperatures at a given  $V_{\rm DS}$  display similar trench widths at sufficiently large  $V_{\rm DS}$  ( $V_{\rm DS}/L_{\rm ch} > 1$  V  $\mu$ m<sup>-1</sup>). Figure 2e presents results for the second SWNT from the right, extracted from Fig. 2a and the bottom frame of Fig. 2b. Clearly, the variations (between the mean value and maximum value) in expansion measured along the length of the SWNT are much larger than those in the trench widths  $(W_{Tc})$ , as quantified by separations between the raised regions of thermocapillary resist at the edges of the trench. This physics provides an ability to realize trenches with small, uniform widths, even across large-scale arrays that incorporate m-SWNTs with wide ranges of conductances and diameters, and consequently, peak temperatures and thermal gradients. Figure 2f shows the average  $W_{Tc}$  for a number of different, individual SWNTs as a function of  $Q_0$ . Similar values occur over ranges of power ( $\sim 10-40 \,\mu W \,\mu m^{-1}$ ) that exceed those associated with

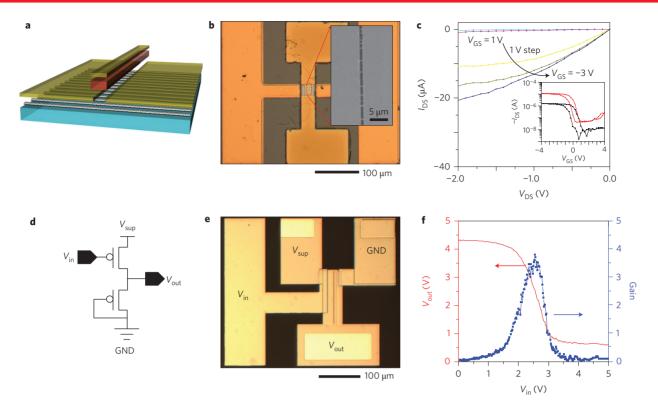

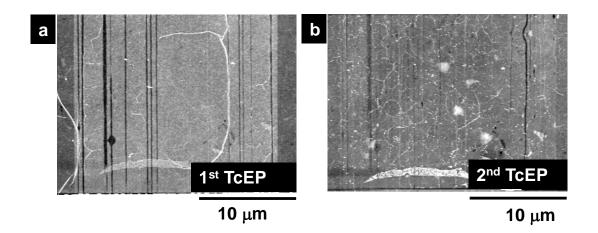

**Figure 5 | Thermocapillary purification process performed with a reusable bottom split gate structure. a**, Schematic illustration of two purification processes implemented on different arrays of SWNTs using a single bottom split gate electrode structure. (i) As-grown array of aligned SWNTs. (ii) Bottom electrode after transfer of these SWNTs (gate dielectric, red; source and drain electrodes, gold; gate electrode, gold). (iii) s-SWNTs remaining after purification. (iv) Transfer of s-SWNTs to a device substrate. **b**, Transfer characteristics before and after a first purification process with a bottom electrode structure:  $I_{on,a}/I_{on,b} = 23\%$  and the on/off ratio after purification is  $\sim 1 \times 10^4$ . **c**, Transfer characteristics before and after a second purification process with the same bottom electrode structure:  $I_{on,a}/I_{on,b} = 30\%$  and the on/off ratio is  $\sim 2 \times 10^4$ . This reusable structure has  $W = L = 30 \mu m$ .

optimized conditions for purification. This behaviour is much different from that expected from other thermally driven processes, such as sublimation or ablation, which typically involve abrupt temperature thresholds (Supplementary Fig. S13).

The governing equation of motion for thermocapillarity in systems where the dimension along the SWNTs can be considered infinite corresponds to unidirectional flow in which the thickness profile in the thermocapillary resist can be written as h(x,t) with

$$\frac{\partial \bar{h}}{\partial \bar{t}} + \frac{\partial}{\partial \bar{x}} \left[ \frac{\bar{\tau} \bar{h}^2}{2\bar{\mu}} + \frac{\bar{h}^3}{3\bar{\mu}} \frac{\partial}{\partial \bar{x}} \left( \bar{\gamma} \frac{\partial^2 \bar{h}}{\partial \bar{x}^2} \right) \right] = 0$$

(2)

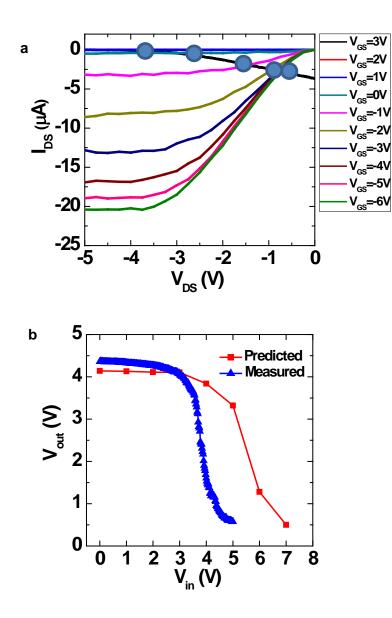

**Figure 6 | Short channel transistors and logic gates that use s-SWNT arrays created by thermocapillary purification. a**, Schematic illustration of the geometry of a short channel ( $L \approx 800$  nm) transistor that incorporates an array of s-SWNTs formed by the thermocapillary purification process (~10 s-SWNTs). b, Optical micrograph and scanning electron microscope image of the device (taken before deposition of the gate dielectric). c, Output characteristics for gate bias of  $V_{GS} = -3$ , -2, -1, 0, 1 V and  $V_{DS} = -2$  to 0 V. Inset: transfer characteristics for  $V_{DS} = -0.1$  V (black) and -1 V (red). d,e, Circuit diagram (d) and optical micrograph (e) of an inverter formed with two transistors that use arrays of s-SWNTs formed by thermocapillary purification. f, Voltage transfer characteristics of the inverter.

where  $\bar{h} = h/h_{\rm f}$ ,  $\bar{x} = x/h_{\rm f}$ ,  $\bar{t} = \gamma_1 Q_0 t/(\mu_0 k_{\rm f} h_{\rm f})$ ,  $\bar{\mu} = \mu/\mu_0$ ,  $\bar{\gamma} = k_{\rm f} \gamma/(Q_0 \gamma_1)$ ,  $\bar{\theta} = k_{\rm f} \theta/Q_0$ ,  $\bar{\tau} = \partial \bar{\theta}/\partial \bar{x}$  is the thermocapillary stress,  $\mu$  is viscosity at temperature T,  $\mu_0$  is the viscosity at the background temperature  $T = T_{\infty}$ ,  $\gamma$  is the surface tension, which often exhibits a linear dependence on temperature (that is,  $\gamma = \gamma_0 - \gamma_1 \theta$  and the bars over symbols indicate the normalized nondimensional variables. Figure 3a shows the geometry. The appropriate initial condition is  $\bar{h}(\bar{x}, \bar{t}=0) = 1$ . The boundary  $\bar{h}(\bar{x} = \pm \infty, \bar{t}) = 1$  and zero conditions are pressure,  $(\partial^2 \bar{h} / \partial \bar{x}^2)(\bar{x} = \pm \infty, \bar{t}) = 0$ . With equation (1) for the temperature, numerical solutions to this system yield  $\bar{h} = h/h_f$ , based on assumptions that (i) at each point along x, the temperature throughout the thickness of the thermocapillary resist is equal to the temperature at its interface with the substrate and (ii) flow in the thermocapillary resist does not change the temperature distributions. Figure 3b shows results for the case of polystyrene<sup>41</sup>, which exhibits behaviours like the thermocapillary resist (Supplementary Fig. S12) but has a known temperature-dependent surface tension:  $\gamma = 50.40 - 0.0738 \theta$  mJ m<sup>-2</sup>. For this example,  $\bar{\mu} = 1$ , consistent with the small rise in temperature, and  $Q_0 = 16.7 \ \mu\text{W} \ \mu\text{m}^{-1}$ (from experiment). The trenches gradually widen and deepen with time, as the displaced material forms ridges at the edges. Topographical measurements of a representative SWNT coated with thermocapillary resist after Joule heating for various time intervals  $(V_{\rm DS}/L_{\rm ch} \approx 0.7 \text{ V } \mu \text{m}^{-1}, 30 \,^{\circ}\text{C}$  background heating, Supplementary Movie S1) show similar behaviours and profiles (Fig. 3c,d). At longer times, wider trenches result, to the point where SWNTs can be clearly observed at the base (Fig. 3e). Although the specific time durations needed to form complete trenches ( $\bar{t} \approx 1$ ) yield computed values of  $W_{\rm Tc}$  that are larger than those observed experimentally, the theory captures the

essential time dependence. For example, Fig. 3f shows the measured time dependence of  $W_{\rm Tc}$  for two SWNTs; both roughly follow the expected theoretical behaviour, namely  $W_{\rm Tc} \approx t^{0.25}$  (Supplementary Figs S7–S9 and Supplementary Movie S1). Another prediction of the theory is that, for a given time t = 300 s, the value of  $W_{\rm Tc}$  depends only weakly on  $Q_0$  over a remarkably large range, that is, from ~10  $\mu$ W  $\mu$ m<sup>-1</sup> to ~35  $\mu$ W  $\mu$ m<sup>-1</sup> (Supplementary Fig. S9). This finding is consistent with observations discussed in the context of Fig. 2. Finally, besides capturing the underlying physics, these models also suggest that optimal materials properties for thermocapillary resists include large temperature coefficients of surface tension and low viscosities. Furthermore, decreasing the thickness reduces the trench widths. Empirical studies of various materials for thermocapillary resists (Supplementary Fig. S12) led to the selection of the molecular glass reported here.

### Application of the purification process

The envisioned use of thermocapillary-enabled purification is in a preparatory mode, where it serves as one of several steps including substrate cleaning, SWNT growth, transfer, and others that occur before device processing. Such a scheme decouples purification from any detailed consideration of component or circuit layout, and is made possible by the ability to entirely eliminate all m-SWNTs. Two approaches can be considered. In the first, one or a small number of electrode structures, each with large lateral extent as illustrated in Fig. 4a.b, enable elimination of m-SWNTs over significant areas. Here, processing occurs on hundreds or thousands of SWNTs at once, using pulsed currents to avoid cumulative heating (Supplementary Fig. S11). Figure 4c shows the electrical characteristics of the structure in Fig. 4a before and after purification, where  $I_{on,a}/I_{on,b}$  is ~20% and the on/off ratio after the process is ~1 × 10<sup>3</sup>,

similar to the results achieved on small arrays discussed previously. Current outputs can reach the milliamp range, as shown in Fig. 4c and Supplementary Fig. S23. Additional details and examples of outputs up to ~3 mA appear in Supplementary Fig. S24. Figure 4d illustrates an alternative approach, in which smaller pairs of interconnected electrodes provide for purification in distributed regions, capable of lithographic alignment at a coarse level to areas of interest in a final application. Effects on  $I_{\rm on}$  and  $I_{\rm off}$  in this case are in the range of those achieved in other geometries (Supplementary Fig. S15, Table S2). The process can be applied to arrays of SWNTs that have both local (Supplementary Fig. S14) and area-averaged (Supplementary Fig. S11) densities of a few per micrometer. Improved densities can be realized using transfer techniques<sup>42-44</sup>. Although high densities can be important in electronics, modest or low densities can be useful in sensors and other devices.

To simplify implementation, a reusable bottom electrode structure can be constructed to eliminate cycles of processing that would otherwise be necessary for the repetitive fabrication of top electrode structures described previously. As shown in Fig. 5a, a single, reusable substrate provides a fully formed, bottom split gate structure for use in the purification process. Aligned arrays of SWNTs transferred to this substrate using techniques described previously<sup>42–44</sup> can be processed to remove m-SWNTs. The remaining s-SWNTs can then be transferred to a final device substrate. Figure 5a schematically illustrates two cycles of this process. Figure 5b,c presents transfer characteristics of arrays of SWNTs before and after purification, performed with a single back-gate structure in two separate cycles of use. Additional details appear in Supplementary Figs S19 and S20.

Because the purification occurs on entire arrays SWNTs, the resulting s-SWNTs can be easily integrated into nearly any type of component or circuit layout. Devices with short channel lengths (~800 nm) defined using a near-field phase-shift lithography technique<sup>45</sup> were used to provide a demonstration, as shown in Fig. 6a,b. Figure 6c presents electrical properties that are consistent with those of long-channel devices when effects of contact resistance are included. The observed hysteresis has known origins that can be minimized using strategies described elsewhere<sup>46-49</sup>. A simple logic gate, consisting of two transistors using arrays of s-SWNTs, provides an additional example of the utility of this process, as illustrated in Fig. 6d,e. Figure 6f shows the voltage transfer characteristics and gain associated with this p-type inverter. The peak gain is ~4, consistent with expectation for this design (Supplementary Figs S16 and S17).

### Conclusions

In summary, the purification method introduced here provides scalable and efficient means for converting heterogeneous arrays of SWNTs into those with purely semiconducting character. An important advantage is that the processing steps are fully compatible with fabrication tools used for the commercial manufacture of digital electronics and display backplanes. Enhanced control might also allow refined forms of purification, based not just on differences between m-SWNTs and s-SWNTs, but also on values of threshold voltage or other more subtle characteristics among the s-SWNTs themselves. Other promising opportunities for future work include the development of schemes for purifying high-density arrays, and for eliminating the need for electrode structures by electromagnetically induced heating in spectral ranges where m-SWNTs exhibit stronger absorption than s-SWNTs.

#### Methods

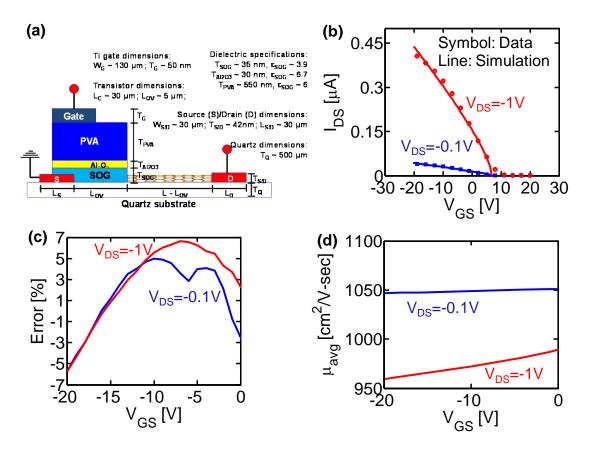

**Fabricating top-electrode structures.** Photolithography, electron-beam evaporation (2 nm Ti, 48 nm Pd; AJA) and liftoff were used to define source and drain electrodes. RIE (100 mtorr, 20 s.c.c.m.  $O_2$ , 100 W, 30 s; Plasma-Therm) removed SWNTs everywhere except for regions between these electrodes. Prebaking (250 °C, 2 h, in a glovebox) a spin-cast (4,000 r.p.m., 60 s) solution to a spin-on glass

(SOG; Filmtronics, methylsiloxanes 215F, 15:1 diluted in isopropyl alcohol)<sup>50</sup> and then curing the material formed films of SOG (35 nm) uniformly across the substrate. Atomic layer deposition (80 °C; Cambridge NanoTech) created films of Al<sub>2</sub>O<sub>3</sub> (30 nm) on top of the SOG. Photolithography (AZ 5214) and etching (6:1 buffered oxide etchant for 50 s) removed the SOG/Al<sub>2</sub>O<sub>3</sub> bilayer from the region between the source and drain electrodes. Prebaking (110 °C, 10 min) a spin-cast (4,000 r.p.m., 60 s) solution of polyvinyl alcohol (PVA;  $M_w$  between 89,000 and 98,000, 99%, hydrolysed, Sigma-Aldrich; solvent, deionized water) mixed with photosensitizer (ammonium dichromate, >99.5% at 40:1 by weight<sup>49</sup>) followed by photolithographic patterning and postbaking (110 °C, 30 min) defined a layer of PVA (~400 nm) on top of and aligned to the SOG/Al<sub>2</sub>O<sub>3</sub>. Photolithography (AZ 5214), electron-beam evaporation (50 nm Ti or Cr) and liftoff were then used to define a gate electrode on top of this dielectric stack.

Thermocapillary flow and etching to remove m-SWNTs. Thermal evaporation (0.5Ås<sup>-1</sup>) was used to form thin layers (25 nm) of thermocapillary resist ( $\alpha,\alpha,\alpha'$ -tris(4-hydroxyphenyl)-1-ethyl-4-isopropylbenzene; TCI International). Applying a voltage between the source and drain electrodes ( $V_{\rm DS} = -40$  to -50 V, corresponding to fields of  $V_{\rm DS}/L_{\rm ch} \approx 1.33-1.66$  V  $\mu$ m<sup>-1</sup>) while biasing the source/gate to +20 V under vacuum ( $\sim 1 \times 10^{-4}$  torr, Lakeshore) and holding the substrate temperature at 60 °C, all for  $\sim 5$  min, yielded trenches in the thermocapillary resist at the locations of the m-SWNTs. RIE (10 mtorr, 1 s.c.c.m. O<sub>2</sub>, 1 s.c.c.m. CF<sub>4</sub>, 75 W, 20 s; Plasma-Therm RIE) eliminated the m-SWNTs exposed in this manner, without affecting the s-SWNTs. Immersion in acetone for 30 min removed the thermocapillary resist, to complete the process.

Scanning Joule expansion microscopy. Devices were wire-bonded to a sample holder (Spectrum Semiconductor Materials) to allow contact-mode AFM (Asylum MFP 3D and Cantilever Asylum # Olympus AC240TS) while applying suitable biases to the electrode structures. A function generator (Agilent 33250A) provided the a.c. bias and the reference signal for lock-in (Stanford SR844) detection of the amplitude and phase of the signal associated with thermal expansion. Measurements on quartz were performed with thick layers (~100 nm) of thermocapillary resist deposited on arrays of SWNTs between two electrodes (that is, two-terminal devices with  $L = 30 \ \mu\text{m}$  and  $W = 30 \ \mu\text{m}$ ). The bias consisted of a sinusoidal voltage with amplitude of 5 V and frequency of 386 kHz. Measurements on SIO<sub>2</sub>(200 nm)/Si were carried out with similar two-terminal devices, but with spin-cast overcoats of poly(methylmethacrylate) (Microchem 950 A2) with thicknesses of ~120 nm. The bias in such cases consisted of a sinusoidal voltage with amplitude of 3 V and frequency of 30 kHz, with the substrate electrically grounded.

Studying the kinetics of thermocapillary flow. Thermal evaporation formed thin layers of thermocapillary resist (~25 nm) on two-terminal devices ( $L = 30 \,\mu$ m,  $W = 100 \,\mu$ m) configured for electrical connection while in the AFM (Asylum Research ORCA sample mount). Images collected by fast scanning (~30 s acquisition times) defined the topography of a small region of interest. Between scans, application of electrical biases for durations short compared to the normalized flow rates (0.1 s at short times and increasing to 30 min at long times) caused the trenches to increase in width by controlled amounts. A total of ~400 scans, corresponding to the device being under bias for a total accumulated time of ~8 h, revealed the kinetics of trench formation throughout and well beyond the time of interest.

**Fabricating reusable bottom electrode structures.** Photolithography and etching defined gate electrodes (2 nm Cr and 13 nm Pd). A bilayer of silicon nitride (STS 200 nm by plasma-enhanced chemical vapour deposition) and SOG (35 nm)<sup>45</sup> served as a gate dielectric. Source and drain electrodes (2 nm Cr and 13 nm Pd) were formed using the same procedures as those for the gate, thereby completing the fabrication.

**Finite-element modelling of heat flow.** The three-dimensional finite-element model for the temperature distributions used eight-node, hexahedral brick elements in a finite-element software package (ABAQUS) to discretize the geometry. The SWNT was treated as a volume heat source, with a zero heat flux boundary at the top surface of Tc-resist, and a constant temperature  $T_{\infty}$  at the bottom of the quartz substrate.

**Numerical modelling of thermocapillary flows.** The equations of motion represent a pair of coupled partial differential equations

$$\frac{\partial \bar{h}_1}{\partial \bar{t}} = \frac{\partial}{\partial \bar{x}} \left( -\frac{\bar{\tau} \bar{h}_1^2}{2\bar{\mu}} - \frac{\bar{h}_1^3}{3\bar{\mu}} \frac{\partial \bar{\gamma}}{\partial \bar{x}} \bar{h}_2 - \frac{\bar{h}_1^3 \bar{\gamma}}{3\bar{\mu}} \frac{\partial \bar{h}_2}{\partial \bar{x}} \right)$$

$$\frac{\partial^2 \bar{h}_1}{\partial \bar{x}^2} - \bar{h}_2 = 0$$

where  $\bar{h}_1 = \bar{h}$ . The boundary conditions are  $\bar{h}_1(\bar{x}, \bar{t} = 0) = 1$   $\bar{h}_2(\bar{x}, \bar{t} = 0) = 0$ ,  $\bar{h}_1(\bar{x} = \pm \infty, \bar{t}) = 1$  and  $\bar{h}_2(\bar{x} = \pm \infty, \bar{t}) = 0$ . A Fortran routine (PDE\_1D\_MG) was used to solve these two partial differential equations directly.

and

Received 22 August 2012; accepted 14 March 2013; published online 28 April 2013

#### References

- Franklin, A. D., Lin, A., Wong, H. S. P. & Chen, Z. Current scaling in aligned carbon nanotube array transistors with local bottom gating. *IEEE Electron. Dev. Lett.* **31**, 644–646 (2010).

- Zhou, X., Park, J-Y., Huang, S., Liu, J. & McEuen, P. L. Band structure, phonon scattering, and the performance limit of single-walled carbon nanotube transistors. *Phys. Rev. Lett.* **95**, 146805 (2005).

- 3. Kang, S. J. et al. High-performance electronics using dense, perfectly aligned arrays of single-walled carbon nanotubes. *Nature Nanotech.* 2, 230–236 (2007).

- Kocabas, C. *et al.* Radio frequency analog electronics based on carbon nanotube transistors. *Proc. Natl Acad. Sci. USA* 105, 1405–1409 (2008).

- Nougaret, L. et al. 80 GHz field-effect transistors produced using high purity semiconducting single-walled carbon nanotubes. Appl. Phys. Lett. 94, 243505 (2009).

- 6. Wang, C. *et al.* Extremely bendable, high-performance integrated circuits using semiconducting carbon nanotube networks for digital, analog, and radio-frequency applications. *Nano Lett.* **12**, 1527–1533 (2012).

- Cao, Q. et al. Medium-scale carbon nanotube thin-film integrated circuits on flexible plastic substrates. Nature 454, 495–500 (2008).

- Sun, D-M. *et al.* Flexible high-performance carbon nanotube integrated circuits. *Nature Nanotech.* 6, 156–161 (2011).

- Snow, E. S., Perkins, F. K., Houser, E. J., Badescu, S. C. & Reinecke, T. L. Chemical detection with a single-walled carbon nanotube capacitor. *Science* 307, 1942–1945 (2005).

- Arnold, M. S., Green, A. A., Hulvat, J. F., Stupp, S. I. & Hersam, M. C. Sorting carbon nanotubes by electronic structure using density differentiation. *Nature Nanotech.* 1, 60–65 (2006).

- Green, A. A. & Hersam, M. C. Nearly single-chirality single-walled carbon nanotubes produced via orthogonal iterative density gradient ultracentrifugation. *Adv. Mater.* 23, 2185–2190 (2011).

- 12. Zheng, M. & Semke, E. D. Enrichment of single chirality carbon nanotubes. J. Am. Chem. Soc. 129, 6084–6085 (2007).

- Liu, H., Nishide, D., Tanaka, T. & Kataura, H. Large-scale single-chirality separation of single-wall carbon nanotubes by simple gel chromatography. *Nature Commun.* 2, 1–8 (2011).

- 14. Wu, J. et al. Short channel field-effect transistors from highly enriched semiconducting carbon nanotubes. Nano Res. 5, 388–394 (2012).

- Krupke, R., Hennrich, F., van Löhneysen, H. & Kappes, M. M. Separation of metallic from semiconducting single-walled carbon nanotubes. *Science* 301, 344–347 (2003).

- Tu, X., Manohar, S., Jagota, A. & Zheng, M. DNA sequence motifs for structure-specific recognition and separation of carbon nanotubes. *Nature* 460, 250–253 (2009).

- Li, X. *et al.* Langmuir–Blodgett assembly of densely aligned single-walled carbon nanotubes from bulk materials. *J. Am. Chem. Soc.* 129, 4890–4891 (2007).

- Engel, M. et al. Thin film nanotube transistors based on self-assembled, aligned, semiconducting carbon nanotube arrays. ACS Nano 2, 2445–2452 (2008).

- LeMieux, M. C. et al. Self-sorted, aligned nanotube networks for thin-film transistors. Science 321, 101–104 (2008).

- Wang, C., Ryu, K., Badmaev, A., Zhang, J. & Zhou, C. Metal contact engineering and registration-free fabrication of complementary metal–oxide semiconductor integrated circuits using aligned carbon nanotubes. ACS Nano 5, 1147–1153 (2011).

- Patil, N. et al. Wafer-scale growth and transfer of aligned single-walled carbon nanotubes. *IEEE Trans. Nanotechnol.* 8, 498–504 (2009).

- Zhou, W., Rutherglen, C. & Burke, P. Wafer scale synthesis of dense aligned arrays of single-walled carbon nanotubes. *Nano Res.* 1, 158–165 (2008).

- Kocabas, C., Kang, S. J., Ozel, T., Shim, M. & Rogers, J. A. Improved synthesis of aligned arrays of single-walled carbon nanotubes and their implementation in thin film type transistors. *J. Phys. Chem. C* 111, 17879–17886 (2007).

- 24. Huang, H., Maruyama, R., Noda, K., Kajiura, H. & Kadono, K. Preferential destruction of metallic single-walled carbon nanotubes by laser irradiation. *J. Phys. Chem. B* **110**, 7316–7320 (2006).

- Collins, P. G., Arnold, M. S. & Avouris, P. Engineering carbon nanotubes and nanotube circuits using electrical breakdown. *Science* 292, 706–709 (2001).

- Balasubramanian, K., Sordan, R., Burghard, M. & Kern, K. A selective electrochemical approach to carbon nanotube field-effect transistors. *Nano Lett.* 4, 827–830 (2004).

- Banerjee, S. & Wong, S. S. Demonstration of diameter-selective reactivity in the sidewall ozonation of SWNTs by resonance Raman spectroscopy. *Nano Lett.* 4, 1445–1450 (2004).

- Hu, H. *et al.* Sidewall functionalization of single-walled carbon nanotubes by addition of dichlorocarbene. *J. Am. Chem. Soc.* **125**, 14893–14900 (2003).

NATURE NANOTECHNOLOGY | VOL 8 | MAY 2013 | www.nature.com/naturenanotechnology

- 29. Pop, E. The role of electrical and thermal contact resistance for Joule breakdown of single-wall carbon nanotubes. *Nanotechnology* **19**, 295202 (2008).

- Javey, A. et al. High-field quasiballistic transport in short carbon nanotubes. Phys. Rev. Lett. 92, 106804 (2004).

- Xiao, J. et al. Alignment controlled growth of single-walled carbon nanotubes on quartz substrates. Nano Lett. 9, 4311–4319 (2009).

- Liao, A., Zhao, Y. & Pop, E. Avalanche-induced current enhancement in semiconducting carbon nanotubes. *Phys. Rev. Lett.* 101, 256804 (2008).

- 33. Liao, A. *et al.* Thermal dissipation and variability in electrical breakdown of carbon nanotube devices. *Phys. Rev. B* **82**, 205406 (2010).

- Ryu, K. *et al.* CMOS-analogous wafer-scale nanotube-on-insulator approach for submicrometer devices and integrated circuits using aligned nanotubes. *Nano Lett.* 9, 189–197 (2008).

- Davis, S. H. Thermocapillary instabilities. Annu. Rev. Fluid Mech. 19, 403–435 (1987).

- Dai, J. et al. Molecular glass resists for high-resolution patterning. Chem. Mater. 18, 3404–3411(2006).

- Islam, A. E. *et al.* Effect of variations in diameter and density on the statistics of aligned array carbon-nanotube field effect transistors. *J. Appl. Phys.* 111, 054511 (2012).

- Saito, R., Dresselhaus, G. & Dresselhaus, M. S. Physical Properties of Carbon Nanotubes (World Scientific, 1998).

- Varesi, J. & Majumdar, A. Scanning Joule expansion microscopy at nanometer scales. *Appl. Phys. Lett.* 72, 37–39 (1998).

- Grosse, K. L., Bae, M-H., Lian, F., Pop, E. & King, W. P. Nanoscale Joule heating, Peltier cooling and current crowding at graphene-metal contacts. *Nature Nanotech.* 6, 287–290 (2011).

- Wulf, M., Michel, S., Jenschke, W., Uhlmann, P. & Grundke, K. A new method for the simultaneous determination of surface tension and density of polymer melts. *Phys. Chem. Chem. Phys.* **1**, 3899–3903 (1999).

- 42. Shulaker, M. *et al.* Linear increases in carbon nanotube density through multiple transfer technique. *Nano Lett.* **11**, 1881–1886 (2011).

- Kang, S. J. et al. Printed multilayer superstructures of aligned single-walled carbon nanotubes for electronic applications. Nano Lett. 7, 3343–3348 (2007).

- 44. Wang, C. *et al.* Synthesis and device applications of high-density aligned carbon nanotubes using low-pressure chemical vapor deposition and stacked multiple transfer. *Nano Res.* **3**, 831–842 (2010).

- 45. Maria, J., Malyarchuk, V., White, J. & Rogers, J. A. Experimental and computational studies of phase shift lithography with binary elastomeric masks. *J. Vac. Sci. Technol. B* 24, 828–835 (2006).

- 46. Jin, S. H. et al. Sources of hysteresis in carbon nanotube field-effect transistors and their elimination via methylsiloxane encapsulants and optimized growth procedures. Adv. Funct. Mater. 22, 2276–2284 (2012).

- Kim, W et al. Hysteresis caused by water molecules in carbon nanotube fieldeffect transistors. Nano Lett. 3, 193–198 (2003).

- Hur, S-H. *et al.* Organic nanodielectrics for low voltage carbon nanotube thin film transistors and complementary logic gates. *J. Am. Chem. Soc.* 127, 13808–13809 (2005).

- Weitz, R. T. *et al.* High-performance carbon nanotube field effect transistors with a thin gate dielectric based on a self-assembled monolayer. *Nano Lett.* 7, 22–27 (2007).

- Jin, S. H. *et al.* Pentacene OTFTs with PVA gate insulators on a flexible substrate. *J. Kor. Phys. Soc.* 44, 181–184 (2004).

#### Acknowledgements

The authors thank C. Lee, M. Losego and D. Cahill for their help with materials characterization. The work at University of Illinois was supported by a grant from the Materials Structures and Devices (MSD) program of the Semiconductor Research Corporation and Northrop Grumman. The facilities were supported by the US Department of Energy, Division of Materials Sciences (award no. DEFG02-91ER45439), through the Frederick Seitz MRL and Center for Microanalysis of Materials at the University of Illinois at Urbana-Champaign. S.N.D. acknowledges support from a National Science Foundation Graduate Research Fellowship.

#### Author contributions

S.H.J., S.N.D. and J.A.R. conceived and designed the experiments. S.H.J., S.N.D., X.X., A.I., J.K., F.D., J.S., J.F., M.M., E.C. and K.G. performed the experiments. J.S., C.L., Y.L., F.X., M.A.W., M.A.A. and Y.H. performed modelling and simulations. E.P., M.A.A., B.K., Y.H. and J.A.R. provided technical guidance. S.H.J., S.N.D., X.X., J.S., Y.H. and J.A.R. analysed the experiments and simulations. S.H.J., S.N.D., J.S. and J.A.R. wrote the manuscript.

#### Additional information

© 2013 Macmillan Publishers Limited. All rights reserved.

Supplementary information is available in the online version of the paper. Reprints and permissions information is available online at www.nature.com/reprints. Correspondence and requests for materials should be addressed to J.A.R.

#### Competing financial interests

The authors declare no competing financial interests.

### ARTICLES

### Using nanoscale thermocapillary flows to create arrays of purely semiconducting single-walled carbon nanotubes

Sung Hun Jin, Simon N. Dunham, Jizhou Song, Xu Xie, Ji-hun Kim, Chaofeng Lu, Ahmad Islam, Frank Du, Jaeseong Kim, Johnny Felts, Yuhang Li, Feng Xiong, Muhammad A. Wahab, Monisha Menon, Eugene Cho, Kyle L. Grosse, Dong Joon Lee, Ha Uk Chung, Eric Pop, Muhammad A. Alam, William P. King, Yonggang Huang and John A. Rogers

In the original version of this file posted online on 28 April 2013 there were some typos: Author names should have read Muhammad A. Wahab and Kyle L. Grosse. Page 44, last line ' $V_{GS}$ ,  $V_{DS}$  using<sup>22</sup>.' should have read ' $V_{GS}$ ,  $V_{DS}$  using Eq. (22).' On Fig. S1c it should have read 'No trench, image missing'. In Fig. S27 caption: '... $V_{DS}$  = 20 V and, therefore, calculated on/off ratio (that is,  $I_{DS}@V_{GS} = -20 V/I_{DS}@V_{GS} = 20 V$ ) goes down.'; 'parallel-gate FET' should have read 'partial-gate FET'. These errors have been corrected in this file 16 May 2013.

# Using Nanoscale Thermocapillary Flows to Create Purely Semiconducting Arrays of Single Walled Carbon Nanotubes

### (Online Supplementary Information)

Sung Hun Jin<sup>\*</sup>, Simon N. Dunham<sup>\*</sup>, Jizhou Song, Xu Xie, Ji-hun Kim, Chaofeng Lu, Ahmad Islam, Frank Du, Jaeseong Kim, Johnny Felts, Yuhang Li, Feng Xiong, Muhammad A. Wahab, Monisha Menon, Eugene Cho, Kyle L. Grosse, Dong Joon Lee, Ha Uk Chung, Eric Pop, Muhammad A. Alam, William P. King, Yonggang Huang, John A. Rogers

### **Individual SWNT thermocapillary trench experiments**

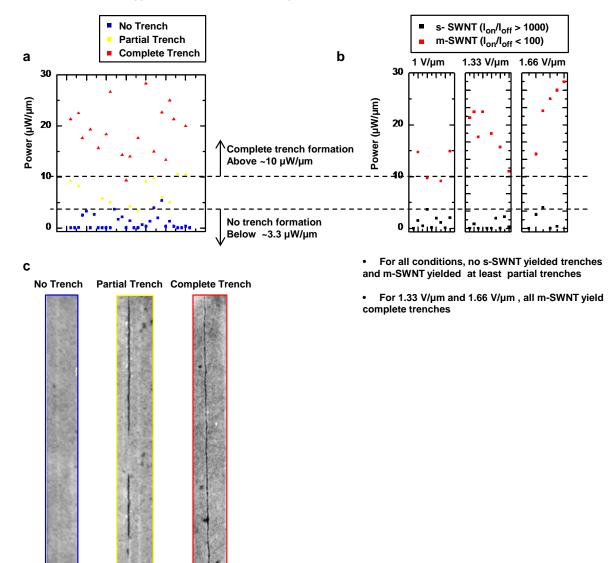

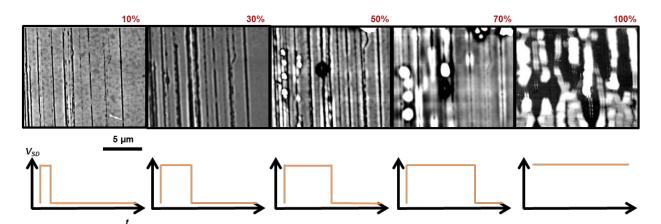

Thermocapillary flows in thermocapillary resists (Tc-resists) were studied (5 min, 60 °C background heating) using devices that incorporate single or several SWNTs. Devices were fabricated in geometries to ensure that only 1 or 2 SWNTs were present in the channel, as confirmed by AFM. In the case of single SWNT devices, the electronic type could be determined directly from the electrical properties (on/off ratio > 100, s-SWNT; on/off ratio < 100, m-SWNT). For devices with 2 SWNTs that exhibited high on/off ratio, both SWNTs must be s-SWNTs. For similar devices with low on/off ratio before thermocapillary enabled purification (TcEP) and high on/off ratio after TcEP, one SWNT must be a m-SWNT and the other a s-SWNT. Devices with two m-SWNTs were not used for these experiments. Biases were applied to increase the resistance of the s-SWNTs (i.e. their "off" state, at +20  $V_{GS}$ ), resulting in relatively low (high) current levels for all s-SWNTs (m-SWNTs). As a result, all 2 SWNT devices fell into one of two cases: their currents were dominated by a single m-SWNT or they contained two s-SWNTs. For the second case, one s-SWNT is likely to dominate, but at worst, the s-SWNT have roughly equal current levels in which case the data served as an upper limit for the actual current and could be as little as half that level. The large number of devices that were studied and the observation that most s-SWNTs showed current levels more than ten times below the threshold for trench formation suggest that assumptions concerning relative current distributions in s-SWNTs are unlikely to affect the broad conclusions. The thresholds were accurately defined by devices with just one SWNT. We performed systematic studies of trenches formed under a range of input powers for single s-SWNTs and single m-SWNTs. A range of outcomes for input powers between 0.1-30  $\mu$ W/ $\mu$ m (SWNT length = 30  $\mu$ m) were observed by AFM (Fig. S1a). For all experiments, powers below 3.3 µW/µm led to no trenches.

2

For powers between 3.3-10  $\mu$ W/ $\mu$ m most devices exhibited trenches, but only partly along the lengths of the SWNTs. For all experiments with powers greater than 10  $\mu$ W/ $\mu$ m, trenches with widths  $W_{Tc}$ ~250-300 nm, were observed along the entire lengths of the SWNTs. This analysis provides information on threshold powers for trench formation, which, via analytical modeling, can be correlated to peak temperatures of ~2-5 °C. By sorting these same results by input field and SWNT electronic type (Fig. S1b), optimized conditions can be established. At fields below the optimal range, the heating is insufficient to yield trenches along the entire lengths of all of the m-SWNTs; at higher fields, the most conductive s-SWNTs begin to show partial trench formation. However, for optimized conditions, all s-SWNTs yielded no trenches, while all m-SWNTs yield complete trenches, as required for proper operation of TcEP.

5 min, 60 °C background,  $V_{GS}$  = +20 V (off state), various  $V_{DS}$

**Figure S1. Critical power for trench formation.** Summary of results on experimental investigations of trench formation (5 min, 60 °C) in devices with single or several SWNT, in which an individual SWNT contributed a majority of the current. The findings define the critical power density to form trenches. All experiments were performed with s-SWNT in their "off" state ( $\pm 20 V_G$ ). (a) Scatter plot of device-level power density associated with the experiments. All devices with power density below 3.3  $\mu$ W/ $\mu$ m show no trenches (blue), all devices with power density above 10  $\mu$ W/ $\mu$ m show complete trenches along the entirety of their length (red), while those with intermediate powers show trenches along part of their length (yellow). Here, local variations in resistance along the length of the SWNT yield powers sufficient for trench formation in some, but not all regions of the SWNT. (b) The same set of experiments, organized by source-drain bias and SWNT electronic type. Although there is a large variation in the power associated with various SWNT at a given bias condition, for optimized conditions (-1.33 and - 1.66 V/ $\mu$ m) all s-SWNT exhibit no trenches, while all m-SWNT exhibit complete trenches along their entire length. (c) Representative AFM images for: no trench (left), partial trench (middle), and complete trench (right) formation.

1 µm

### **Deposition conditions for the Tc-resist and its properties**

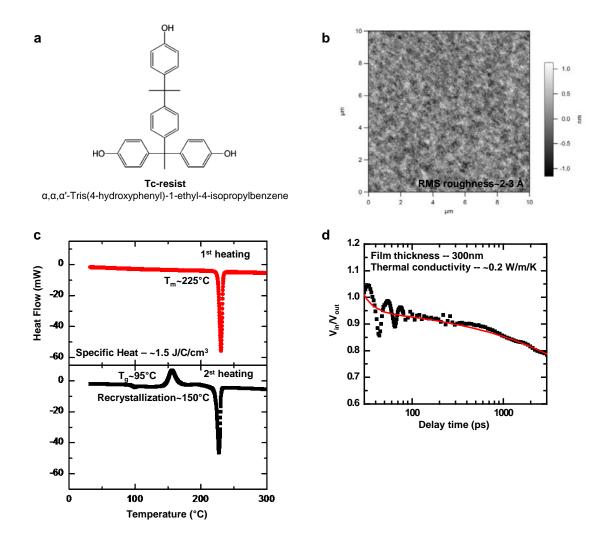

Figure S2a shows the chemical structure of the Tc-resist. The material was deposited via thermal evaporation. Figure S2b shows AFM images of a film deposited on a SiO<sub>2</sub>/Si substrate. The surface roughness is comparable to that of the underlying substrate, i.e. 2-3 Å. Experiments that involved heated substrates (quartz or SiO<sub>2</sub>/Si) with thin coatings of Tc-resist (~25 nm thickness) showed an onset of dewetting between 80-120 °C, depending on substrate hydrophobicity. Clean, hydrophilic surfaces yielded higher dewetting temperatures. In vacuum (~1×10<sup>-4</sup> torr), sublimation began at ~100 °C, as determined by experiments using lithographically patterned, calibrated resistive heaters of Pt (lengths ~1-3 mm, widths ~6-10 µm). Differential Scanning Calorimetry (dry nitrogen) yielded a specific heat of ~1.5 J/C/cm<sup>3</sup> (Fig. S2c, T<sub>m</sub>= 225 °C, T<sub>g</sub>= 95 °C, T<sub>rc</sub>=155 °C). Time resolved, picosecond pump-probe experiments based on thermoreflectance<sup>1</sup> using relatively thick films (300 nm, Fig. S2d) yielded thermal conductivities of ~0.2 W/m/K, similar to most organic thin films. Furthermore, similar experiments with relatively thin films (~25, ~50, ~75 nm), suggest that the thermal interface resistance between quartz and the Tc-resist is ~50-150 MW/m<sup>2</sup>/K.

**Figure S2. Tc-resist characterization.** (a) Chemical structure for Tc-resist. (b) AFM of a pristine film deposited by thermal evaporation (25 nm,  $\sim 1$ Å/s) showing a very smooth surface (2-3 Å RMS roughness, similar to underlying Si substrate). (c) DSC of Tc-resist showing specific heat ( $\sim 1.5$  J/C/cm<sup>3</sup>), melting temperature ( $\sim 225$  °C), recrystallization ( $\sim 150$  °C), and glass transition ( $\sim 95$  °C) for a bulk sample. (d) Thermoreflectance for a 300 nm thick film of Tc-resist. Fitting yields thermal conductivities of  $\sim 0.2$  W/m/K.

### **Single SWNT conductance statistics**

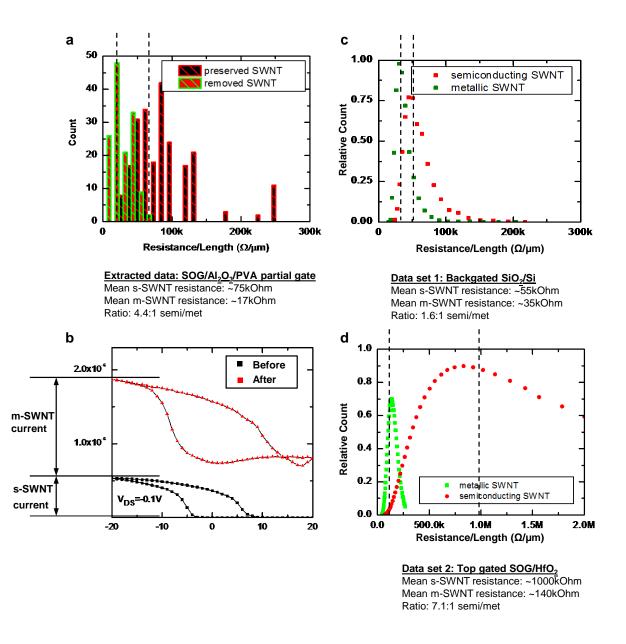

The large number of SWNTs studied by TcEP on devices with small arrays of SWNTs provided statistics on the process. For each array, the number of SWNTs and the values of  $I_{on, b}$  and  $I_{on, a}$  (shown for a typical device, Fig S3b) together with an assumption that all of the removed SWNTs are m-SWNTs and all of the remaining SWNTs are s-SWNTs, yields estimates for the average conductance of these two types of SWNTs, for each device. Figure S3a shows a histogram of the conductances of individual SWNTs determined in this way. (We note that a device with 3 s-SWNTs and an average conductance of 50 k $\Omega$ /µm is counted 3 times.) The mean conductances for m-SWNTs and s-SWNTs (in their on state) are 17 k $\Omega$ /µm and 75 k $\Omega$ /µm, respectively. These distributions are in the range of those reported for single SWNTs studied devices (Fig. S3c)<sup>2</sup>; and 140 k $\Omega$ /µm (m-SWNTs) and 55 k $\Omega$ /µm (s-SWNTs) for top gated devices<sup>2</sup>. Using the experimentally observed ratios of numbers of m-SWNTs to s-SWNTs, and a ratio of mean conductances of ~4:1, the assumption that TcEP preserves all s-SWNT is consistent with observations.

**Figure S3. SWNT resistivity data.** (a) Extracted average resistivity for m-SWNTs and s-SWNTs based on sorted small area arrays. Average resistivity for each of 37 devices based on device resistance changes before and after TcEP and the number of SWNTs removed and remaining (based on AFM). (b) Typical I-V for an array before and after TcEP showing the relative conductance attributed to both m-SWNT and s-SWNT. (c,d) Histograms showing distributions of individual SWNT resistivities for two data sets, one based on back-gated devices on SiO<sub>2</sub>/Si and the other based on top-gated devices with a gate dielectrica of SOG/HfO<sub>2</sub>. Distributions representative of previously published results on arrays of SWNT.

### Partial gate device properties

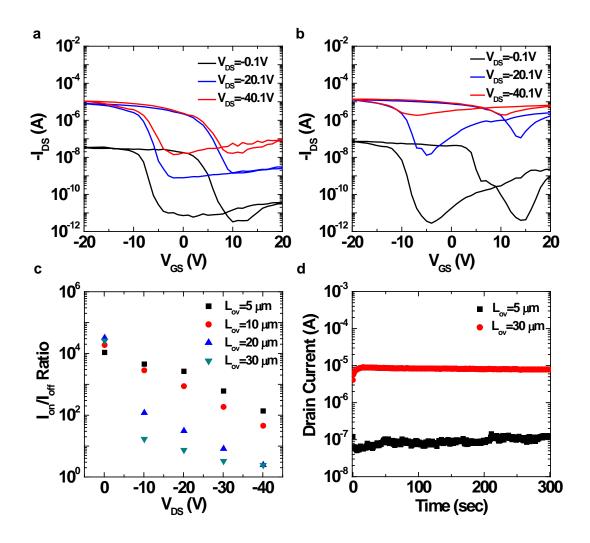

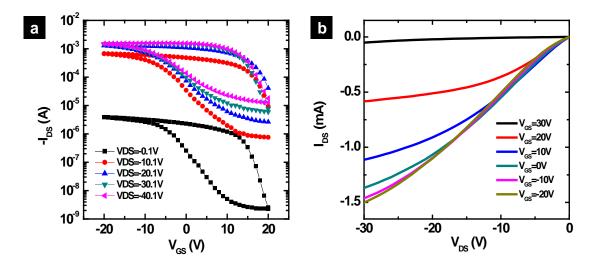

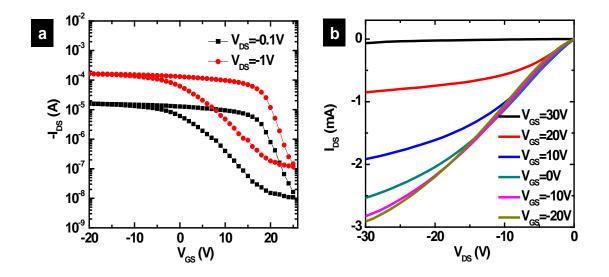

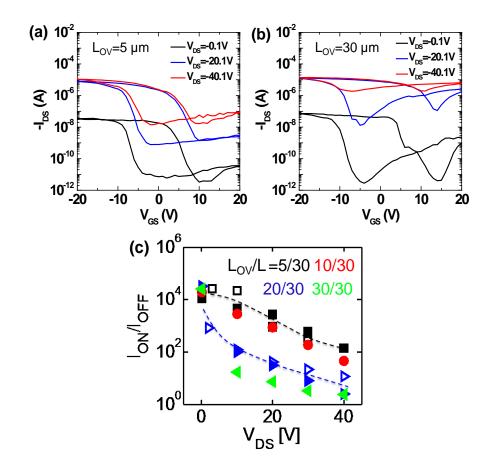

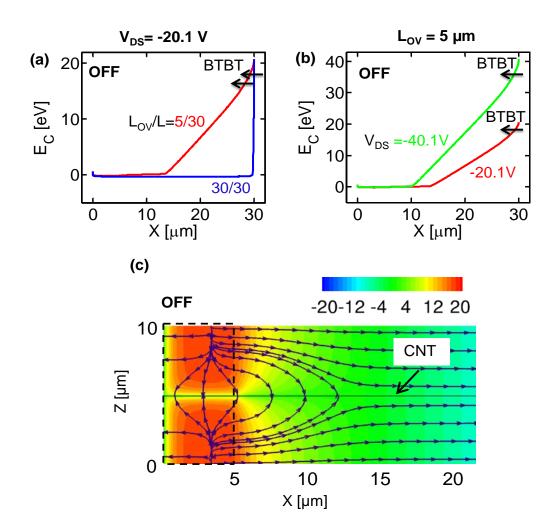

The electrode geometries used for TcEP involved a partial gate structure shown schematically in Fig. 1a. This configuration results in reduced gate-drain fields, which minimize Schottky barrier tunneling, band-to-band tunneling and avalanche phenomena<sup>3</sup>. The operation avoids ambipolar conduction at the bias conditions needed for TcEP (characterization at conditions consistent with TcEP, 60 °C background heating,  $\sim 1 \times 10^4$  torr). These effects are clearly observed in transfer characteristics for devices based on an individual s-SWNT in partial gate (Fig. S4a) and full gate (Fig. S4b) layouts. Here, the same SWNT, same pair of sourcedrain electrodes, and dielectric were used for both devices. The only difference is the length of gate extension into the channel. Both configurations exhibit ideal device behavior at low bias  $(V_{DS}=-0.1 \text{ V})$ . At high bias  $(V_{DS}<-10 \text{ V}, L=30 \text{ }\mu\text{m})$ , however, the full gate device shows pronounced ambipolar conduction, unlike the partial gate case. Figure S3c illustrates the effect of source-drain bias and gate overlap  $(L_{\alpha\nu})$  on on/off ratio, where all measurements were performed on the same SWNT. The device with 5 µm gate overlap (i.e. the configuration used for TcEP) exhibits on/off ratios 2-3 orders of magnitude higher than the device with full overlap  $(L_{\alpha\nu}=30 \text{ }\mu\text{m})$ . Figure S4d shows the ability of the partial gate configuration to maintain current levels several orders of magnitude lower than that of the full gate configuration, even for long bias durations ("off" state,  $V_{DS}$ =-40V,  $V_{GS}$ =+20V, 5 min, consistent with TcEP experiments).

**Figure S4. Effect of partial gate transistor geometry.** Electrical characterization of an individual SWNT device with varying gate overlap. Transfer characteristics for different drain voltages ( $V_{DS}$ =-0.1, -20, -40 V) for the case of (a) partial gate and (b) full gate configurations. (c)  $I_{on}/I_{off}$  dependence on gate overlap ( $L_{ov}$ ) ranging from 5 to 30 µm and (d) drain current associated with devices held in their off state ( $V_{GS}$ =+20 V,  $V_{DS}$ =-40V) for extended durations, for partial gate and full covered configurations.

### **Scanning Joule expansion microscopy**

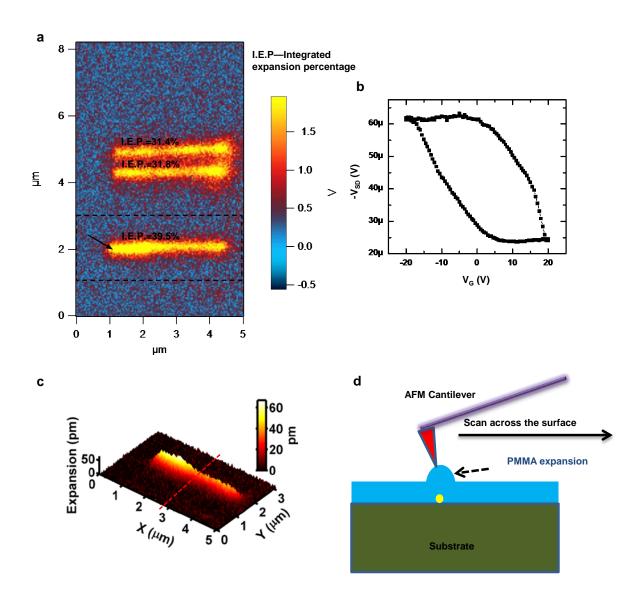

Figure S5a shows a scanning Joule expansion microscope (SJEM) image<sup>4</sup> of an array of SWNTs (two terminal device, SiO<sub>2</sub> (200 nm) / Si substrate) covered with a 120 nm thick film of PMMA, collected at the condition of  $V(t) = V_{DS} \cos(2\pi ft)$  with  $V_{DS}=3$  V and f=30 kHz and  $V_{GS}=0$  V. Figure S5a shows the integrated expansion percentage (I.E.P.). To determine this quantity, we first located the maximum expansion along each measured cross-section perpendicular to the length of the SWNT. Next, we integrated these values along each SWNT, to get the integrated expansion (I.E.). The I.E.P. is the ratio of the I.E. to the sum of the I.E. for all three SWNTs, times 100%. Since the maximum expansion is proportional to the input power, the I.E.P. can be used to estimate the power input for each SWNT, from the measured total power into the device. Figure S5c shows a 3D rendering of the SJEM signal for the SWNT associated with Fig. 2b. Figure S5d shows a schematic of the SJEM measurement.

**Figure S5. Summary of SJEM measurements.** (a) Full SJEM image for an array of 3 SWNTs. The relative integrated intensity for each SWNT is indicated. This relative intensity is used to calculate the relative proportion of the total device power density associated with each SWNT. (b) Transfer characteristic of a device with an array of 3 SWNTs. (c) SJEM image for a SWNT used for validation of analytical temperature models (Fig. 2c). (d) Schematic illustration of SJEM measurements.

### Computed temperature distributions associated with Joule heating in individual SWNTs

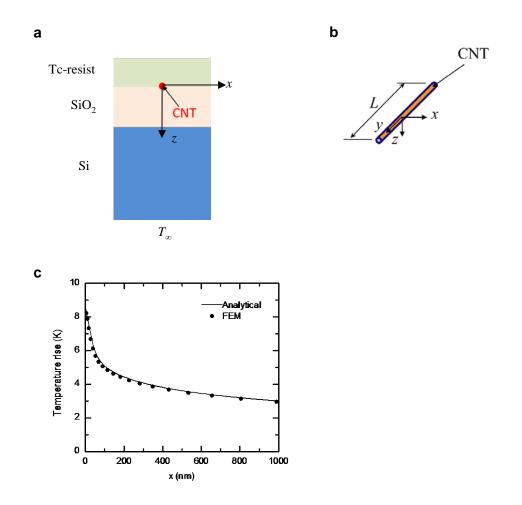

In this section, we describe procedures for determining the temperature distribution resulting from a SWNT embedded in a film of PMMA on SiO<sub>2</sub>/Si substrate with power dissipation at the SWNT for an AC applied voltage. The temperature rise at the surface of the Tc-resist can be obtained by considering first the analytical solution for a disk heat source with radius  $r_0$  at the interface between the Tc-resist and the SiO<sub>2</sub>. Here, a cylindrical coordinate system is set such that the origin is coincident with the center of the heat source as shown in Fig. S6a,b. The heat transfer governing equation temperature in cylindrical coordinate is

$$\frac{\partial^2 T}{\partial r^2} + \frac{1}{r} \frac{\partial T}{\partial r} + \frac{\partial^2 T}{\partial z^2} - \alpha \frac{\partial T}{\partial t} = 0$$

(1)

where  $\alpha = \frac{k}{c\rho}$  is thermal diffusivity, *k* is thermal conductivity,  $\rho$  is density, and *c* is specific heat capacity. The subscripts 0, 1 and 2 denote Tc-resist, SiO<sub>2</sub> and Si, respectively. Setting  $\theta = T - T_{\infty}$ , where  $T_{\infty}$  is the remote temperature, the above equation is equivalent to

$$\frac{\partial^2 \theta}{\partial r^2} + \frac{1}{r} \frac{\partial \theta}{\partial r} + \frac{\partial^2 \theta}{\partial z^2} = \alpha \frac{\partial \theta}{\partial t}$$

(2)

The boundary conditions are

(1)  $z = -h_0$  (top surface)

$$-k_0 \frac{\partial \theta}{\partial z}\Big|_{z=-h_0} = 0 \tag{3}$$

(2) z = 0

$$\theta_{0^+} = \theta_{0^-}, \ -k_0 \frac{\partial \theta}{\partial z}\Big|_{z=0^-} = \begin{cases} Q_1 & 0 \le r \le r_0 \\ Q_{c1} & r_0 < r < +\infty \end{cases}, \ -k_1 \frac{\partial \theta}{\partial z}\Big|_{z=0^+} = \begin{cases} Q_2 & 0 \le r \le r_0 \\ Q_{c1} & r_0 < r < +\infty \end{cases}$$

(4)

where  $Q_1$  and  $Q_2$  satisfy  $-Q_1 + Q_2 = \frac{P}{\pi r_0^2}$ , P is the total power of the disk.

(3)  $z = h_1$

$$\theta_{h_1^+} = \theta_{h_1^-} \text{ and } -k_1 \frac{\partial \theta}{\partial z}\Big|_{z=h_1} = -k_2 \frac{\partial \theta}{\partial z}\Big|_{z=h_1}$$

(5)

$(4) \quad z = h_1 + h_2 \sim \infty$

$$\theta_{h_1+h_2} = 0 \tag{6}$$

For a voltage  $V(t) = V_0 \cos(\omega t)$  with angular frequency  $\omega = 2\pi f$ , the Joule heating has angular frequency  $2\omega$ . The total power of the disk can then be obtained as  $P(t) = P_0 [1 + \cos(2\omega t)]/2$ , which yields a constant temperature rise (DC component) due to  $P_0/2$  and a time oscillating temperature rise (AC component) due to  $P_0 \cos(2\omega t)/2$ . It should be noted that the DC component of temperature rise can be easily obtained by setting  $\omega=0$  in the solution of AC component.

The time oscillating temperature rise (AC component) has the same frequency as the power density, i.e.  $\theta(r, z, t) = \theta(r, z) \exp(2\omega t i)$ . Therefore, we have

$$\frac{\partial^2 \theta}{\partial r^2} + \frac{1}{r} \frac{\partial \theta}{\partial r} + \frac{\partial^2 \theta}{\partial z^2} - q^2 \theta = 0$$

<sup>(7)</sup>

where

$$q^2 = \frac{2\omega i}{\alpha}$$

and  $\theta = \theta(r, z)$ .

Equation (7) can be solved via the Hankel transform, for which the following transform pair of the first kind is applicable,

$$\varphi(r,z) = \int_0^\infty \overline{\varphi}(\xi,z) J_0(\xi r) \xi d\xi$$

$$\overline{\varphi}(\xi,z) = \int_0^\infty \varphi(r,z) J_0(\xi r) r dr$$

(8)

where  $\varphi(r, z)$  is the original function,  $\overline{\varphi}(\xi, z)$  is the transform, and  $J_0$  is the 0<sup>th</sup> order Bessel function of the first kind. Equation (7) then becomes

$$\frac{d^2\overline{\theta}}{dz^2} - (\xi^2 + q^2)\overline{\theta} = 0$$

<sup>(9)</sup>

Solving the above equation gives

$$\overline{\theta} = A \exp(z\sqrt{\xi^2 + q^2}) + B \exp(-z\sqrt{\xi^2 + q^2})$$

(10)

where A and B are two unknown functions to be determined according to boundary and continuity conditions. The temperature rise is then obtained by

$$\theta = \int_0^\infty \left( A \mathrm{e}^{-\xi z} + B \mathrm{e}^{\xi z} \right) J_0(\xi r) \xi \mathrm{d}\xi \tag{11}$$

Therefore, the temperature rise in Hankel space at each layer is obtained as

Tc-resist:

$$\overline{\theta}_0(\xi, z) = A_0 \exp(z\sqrt{\xi^2 + q_0^2}) + B_0 \exp(-z\sqrt{\xi^2 + q_0^2})$$

SiO2 layer:  $\overline{\theta}_{1}(\xi, z) = A_{1} \exp(z\sqrt{\xi^{2} + q_{1}^{2}}) + B_{1} \exp(-z\sqrt{\xi^{2} + q_{1}^{2}})$

15

Si layer:

$$\overline{\theta}_2(\xi, z) = A_2 \exp(z\sqrt{\xi^2 + q_2^2}) + B_2 \exp(-z\sqrt{\xi^2 + q_2^2})$$

With BCs (3)-(6) in Hankel space, we can obtain the temperature at each layer. For example,  $A_0$  and  $B_0$  are given by

$$A_{0} = \frac{\kappa + 1}{\left(1 - \kappa\right) \left[1 + \exp(-2h_{0}\sqrt{\xi^{2} + q_{0}^{2}})\right] + \left(\kappa + 1\right) \frac{k_{0}\sqrt{\xi^{2} + q_{0}^{2}}}{k_{1}\sqrt{\xi^{2} + q_{1}^{2}}} \left[1 - \exp(-2h_{0}\sqrt{\xi^{2} + q_{0}^{2}})\right] \frac{P_{0}}{k_{1}\pi\xi\sqrt{\xi^{2} + q_{1}^{2}}} \frac{J_{1}(\xi r_{0})}{2r_{0}}$$

$$B_{0} = A_{0}\exp(-2h_{0}\sqrt{\xi^{2} + q_{0}^{2}})$$

(12)

where

$$\kappa = \frac{1 - \frac{k_2}{k_1} \frac{\sqrt{\xi^2 + q_2^2}}{\sqrt{\xi^2 + q_1^2}}}{1 + \frac{k_2}{k_1} \frac{\sqrt{\xi^2 + q_2^2}}{\sqrt{\xi^2 + q_1^2}}} \exp(-2h_1\sqrt{\xi^2 + q_1^2})$$

The temperature rise due to the disk heat source can be obtained by Eq. (11). For example, the temperature rise in the Tc-resist is obtained as

$$\theta(r,z) = \int_0^{+\infty} A_0 \left[ \exp(z\sqrt{\xi^2 + q_0^2}) + \exp(-z\sqrt{\xi^2 + q_0^2} - 2h_0\sqrt{\xi^2 + q_0^2}) \right] \cdot J_0(\xi r) \xi d\xi$$

(13)

The surface temperature rise of the Tc-resist is then obtained by setting  $z = -h_0$  as

$$\theta(r) = \int_0^{+\infty} 2A_0 \exp(-h_0 \sqrt{\xi^2 + q_0^2}) \cdot J_0(\xi r) \xi d\xi$$

(14)

As  $r_0 \rightarrow 0$ , we obtain the temperature rise due to a point heat source as

$$\theta_{P}(r) = \frac{1}{4k_{1}\pi} \int_{0}^{+\infty} \frac{(\kappa+1)J_{0}(\xi r)\xi}{(1-\kappa)\cosh(h_{0}\sqrt{\xi^{2}+q_{0}^{2}}) + (\kappa+1)\frac{k_{0}\sqrt{\xi^{2}+q_{0}^{2}}}{k_{1}\sqrt{\xi^{2}+q_{1}^{2}}} \sinh(h_{0}\sqrt{\xi^{2}+q_{0}^{2}})} \cdot \frac{P_{0}}{\sqrt{\xi^{2}+q_{1}^{2}}} d\xi$$

(15)

For a point heat source at  $(0, \eta, 0)$  with heat generation  $P_0 = Q_0 \cdot d\eta$  and  $Q_0$  as the power density, the integration of Eq. (15) with  $r = \sqrt{(\eta - y)^2 + x^2}$  gives the temperature rise at point (x, y)due to a line heat source as

$$\theta(x,y) = \frac{1}{4k_1\pi} \int_{-L/2}^{L/2} d\eta \int_{0}^{+\infty} \frac{(\kappa+1)J_0\left(\xi\sqrt{(\eta-y)^2+x^2}\right)\xi}{(1-\kappa)\cosh(h_0\sqrt{\xi^2+q_0^2}) + (\kappa+1)\frac{k_0\sqrt{\xi^2+q_0^2}}{k_1\sqrt{\xi^2+q_1^2}}\sinh(h_0\sqrt{\xi^2+q_0^2})} \cdot \frac{Q_0}{\sqrt{\xi^2+q_1^2}} d\xi$$

(16)

It should be noted that Eq. (16) gives the magnitude of time oscillating temperature rise, i.e.,  $\theta_0$  in the main text is equal to  $2\theta(x,y)$ . The total surface temperature rise can be obtained as  $\theta(x, y, t) = \theta(x, y)|_{\omega=0} + \theta(x, y)\cos(4\pi ft) = [\theta_1 + \theta_0\cos(4\pi ft)]/2$  due to a line heat source with power density  $Q(t) = Q_0 [1 + \cos(2\omega t)]/2$ .

Here, boundary conditions involve continuous temperature and heat flow at all material interfaces except those with the SWNT, negligible heat flow at the top surface and a constant temperature at the base of the substrate. For the SWNT interface, discontinuous heat flow, is assumed, as a means to introduce the Joule heat source. The results, together with materials constants taken from the literature (see Supplementary Information, Table S1) and analytical treatments of the resulting thermal expansion, yield expansion profiles that have both peak

magnitudes ( $E_0 \sim 50$  pm) and spatial distributions (characteristic widths ~340 nm) that are remarkably consistent with the SJEM results (~40 pm and ~320 nm, respectively), when  $Q_0 \sim 13$  $\mu$ W/ $\mu$ m, the estimated experimental value.

## Computed thermal expansion at the surface of a thin film coating on a heated SWNT on a substrate

Under the assumptions of (1) plane strain in *y* direction since the length of SWNT (~ $30\mu$ m) is much larger than its radius and (2) plane stress in *z* direction since the film is very thin (~25nm), the peak-peak value of AC surface thermal expansion (i.e., the out-of-plane displacement) of the Tc-resist can be obtained as

$$E_0 = \frac{1 + v_0}{1 - v_0} \beta_0 h_0 \theta(x, y = -h_0)$$

(17)

where  $v_0$  and  $\beta_0$  are the Poisson's ratio and coefficient of thermal expansion of the PMMA, respectively.

### Computed temperature distribution for a system consisting of a SWNT undergoing Joule heating with a constant bias, on a quartz substrate coated with Tc-resist

Setting  $k_2 = k_1 = k_s$ ,  $k_0 = k_f$ ,  $h_0 = h_f$  and  $\omega = 0$ , Eq. (16) gives the surface temperature of

Tc-resist for Tc-resist/quartz under DC voltage as

$$\theta(x, y) = \frac{1}{2k_s \pi} \int_{-L/2}^{L/2} d\eta \int_0^\infty \frac{Q_0 J_0 \left(\xi \sqrt{(\eta - y)^2 + x^2}\right)}{\cosh(\xi h_f) + \frac{k_f}{k_s} \sinh(\xi h_f)} d\xi$$

(18)

18

where  $k_f$  and  $k_s$  are the thermal conductivity of Tc-resist and quartz, respectively and  $h_f$  is the thickness of Tc-resist