# Electrostatic Dimension of Aligned-Array Carbon Nanotube Field-Effect Transistors

Muhammad A. Wahab,<sup>†,⊥</sup> Sung Hun Jin,<sup>‡,⊥</sup> Ahmad E. Islam,<sup>‡,#</sup> Jaeseong Kim,<sup>‡</sup> Ji-hun Kim,<sup>‡</sup> Woon-Hong Yeo,<sup>‡</sup> Dong Joon Lee,<sup>‡</sup> Ha Uk Chung,<sup>‡</sup> John A. Rogers,<sup>‡,§</sup> and Muhammad A. Alam<sup>†,\*</sup>

<sup>†</sup>School of Electrical and Computer Engineering, Purdue University, West Lafayette, Indiana 47907, United States, <sup>‡</sup>Department of Materials Science and Engineering and Frederick Seitz Materials Research Laboratory, University of Illinois, Urbana, Illinois 61801, United States, and <sup>§</sup>Departments of Chemistry, Mechanical Science and Engineering, Electrical and Computer Engineering, Beckman Institute for Advanced Science and Technology, University of Illinois, Urbana, Illinois 61801, United States. <sup>⊥</sup>These authors contributed equally to this work. <sup>#</sup>Present address: Soft Matter Materials Branch, Materials and Manufacturing Directoriate, Air Force Research Laboratory, Wright-Patterson Air Force Base, Dayton OH 45433.

**ABSTRACT** Accurate electrostatics modeling of nanotubes (NTs)/nanowires (NWs) has significant implications for the ultimate scalability of aligned-array NT/NW field-effect transistors (FETs). The analysis to date has focused on limits of capacitive coupling between the 1D channel and 2D gate that is strictly relevant only in the linear response operation of NT/NW-FETs. Moreover, the techniques of electrostatic doping by independent gates that cover only part of the channel are widely used, but the nature of its electrostatic coupling has not

been explored. In this paper, we use a three-dimensional, self-consistent model for NT/NW-FETs to interpret the essence of electrostatic coupling with complex configuration of electrode geometries. The interplay between 3D electric fields and its 1D termination onto the NTs/NWs suggests surprising complexity of electrostatic interaction not captured in simpler models. This coupling can change the performance metrics such as 0N and OFF currents by orders of magnitude depending on (1) NT/NW density, (2) bias voltage, and (3) gate overlap length. Remarkably, this parasitic coupling persists regardless of the gate oxide thickness, changes in dielectric constant, and/or the width of the diameter distribution of NTs/NWs. The predictions of the model are systematically validated by a series of experiments.

**KEYWORDS:** aligned-array carbon nanotubes · tube density · partial-gate transistor · three-dimensional electrostatics · parasitic gate coupling · band-to-band tunneling · high field transport

mergence of the nanotubes (such as carbon nanotube, boron nitride nanotube, molybdenum disulfide nanotube, and tungsten disulfide nanotube) and nanowires (such as silicon nanowire, III-V, and II-VI compound semiconductor nanowires) has attracted attention of researchers because of their exclusive 1D structure.<sup>1-3</sup> Interest in nanotube (NT)/ nanowire (NW) electronics has been sustained by a broad range of potential applications (e.g., digital/analog electronics,<sup>4–8</sup> memory,<sup>9,10</sup> display,<sup>11,12</sup> optoelectronics,<sup>8,13,14</sup> and chemical/biosensing<sup>15,16</sup>) enabled by the unique electrical, optical, chemical, topological, and percolative properties of single, array, and networks of NTs/NWs. The essential building blocks in these applications are field-effect transistors (NT/NW-FETs) in three- or four-terminal configurations.<sup>14,17-21</sup> Electrical (e.g., mobility, conductivity, contact resistance, coefficients of impact ioniza-

tion, coefficients of band-to-band tunneling), optical (e.g., quantum yield), and sensing (e.g., sensitivity) parameters extracted in these applications depend on the electrostatic interpretation of gate control on NTs/ NWs. In the traditional approach, the capacitance between the channel and gate is calculated by using two-electrode geometry (where NTs/NWs form lines<sup>4,22</sup> or thin films<sup>4,22,23</sup> on a plane, or are surrounded by a gate in a coaxial geometry<sup>22</sup>) with appropriate correction for NT/NW density.23,24 This presumption of 2D symmetry along the channel direction is generally appropriate for interpreting linear response (low  $V_{DS}$ ) of NT/NW-FET operation, especially with full-gate coverage<sup>4,7,25-29</sup> (Figure 1a). As the drain bias is increased or partial gates (necessary for electrostatic doping<sup>13,14,17,20</sup> and for obtaining better control in conduction for different chiralities<sup>30–32</sup>) are turned on, the 2D symmetry along the channel is

\* Address correspondence to alam@purdue.edu.

Received for review October 16, 2012 and accepted January 15, 2013.

Published online January 16, 2013 10.1021/nn304794w

© 2013 American Chemical Society

VOL.7 • NO.2 • 1299-1308 • 2013

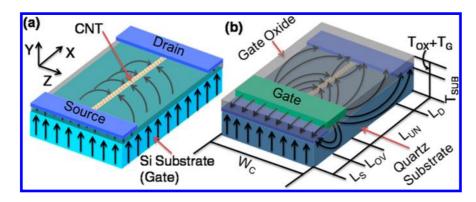

Figure 1. Schematic illustration of the electric field distribution in a (a) full-gate CNTFET (FG-FET) and (b) partial-gate CNTFET (PG-FET), with CNT as the channel. For FG-FET, the gate dictates the electrostatics of CNTs, whereas for PG-FET, the gate controls CNT electrostatics of the entire overlap region (length:  $L_{OV}$ ) and part of the underlap region (length:  $L_{UN}$ ) through parasitic coupling. As we show later, the extent of this coupling depends on CNT density (N). Here,  $W_C = 1/N$  is the electrostatic width shared by one CNT in an array,  $L_{D(S)}$  is the drain (source) length, and  $T_{SUB}$ ,  $T_{OX}$ , and  $T_G$  are the thickness of quartz substrate, gate oxide, and gate contact, respectively.

broken, and the 3D field lines from the electrodes terminate onto quasi-1D NT/NW conductors through fringing fields (Figure 1b). As a result, effective electrostatic dimension that apportions the relative control of gate and drain over the channel (and corresponding performance metrics) of these devices evolves with biasing configuration.<sup>33,34</sup>

In this paper, we use a 3D electrostatic simulation of especially designed partial-gate FETs (PG-FETs) with variable single-wall carbon nanotube (CNT) density to explore the implications of three-dimensional electrostatic coupling between electrodes and NT/NW channels. (Although we analyze the carbon nanotubes in this work, the essential physics and conclusions should also be applicable for other 1D nanotube and nanowire transistors.) Our analysis offers an intuitive interpretation of the evolution of the parasitic gate control (through fringing fields) as a function of biasing configuration, CNT density, and finite size of the electrodes. Irrespective of the gate oxide thickness, dielectric constant, and CNT diameter, our theoretical results show the following: (1) The effect of 3D coupling is most significant for single-tube or low-density arrays (relevant for most experiments published in CNTFET literature), and as a result, the performance metrics such as ON and OFF currents may differ by orders of magnitude from those predicted by traditional 2D electrostatic model. (2) Although parasitic gate-CNT coupling is suppressed with increasing CNT density, the residual coupling is still significant, and therefore, unless the density approaches the charge-sheet limit (>100 CNTs/ $\mu$ m), the OFF state tunneling current cannot be predicted by a 2D model, even for moderately high densities. (3) Device parameters such as mobility, tunneling coefficients, etc., extracted by 2D interpretation of these devices, are likely to be incorrect. Finally, (4) the 2D limit is only approached asymptotically for very high tube density ( $N > 100 \text{ CNTs}/\mu\text{m}$ ).

The paper is organized as follows. In the following section, we use a self-consistent simulation framework

that couples the 3D Poisson equation with the 1D driftdiffusion transport.<sup>35</sup> The drift-diffusion model has been generalized to include tunneling and impact ionization phenomena and carefully calibrated to 1D transport in CNTs. This model is then applied to predict the characteristics of partial-gate FET (PG-FET) as a function of tube density (N), gate overlap length  $(L_{\rm OV})$ , and drain bias  $(V_{\rm DS})$ . We find that the complex electrostatic interaction in a PG-FET results in significant and somewhat counterintuitive variation in ON and OFF currents as a function of device parameters. Theoretical predictions are later validated against a series of experiments. The universality of the model is observed by analyzing the effects of gate oxide thickness ( $T_{OX}$ ), dielectric constant ( $\varepsilon_{OX}$ ), and CNT diameter (d). We conclude the paper with a summary of the analysis and a few comments regarding the generality of our conclusions.

### **RESULTS AND DISCUSSION**

PG-FET Modeling and Simulation Results. The extent of deviation from classical 2D electrostatics and guasi-3D gate control on the electrostatics of PG-FET are simulated by varying  $N \sim 1/W_{\rm C}$  of aligned-array CNTs (Figure 1b), where  $W_{\rm C}$  is the spacing between the CNTs in an array. CNTs with diameter d = 1.74 nm are spaced uniformly with pitch  $W_c$ . Self-consistent solution of the Poisson and drift-diffusion equations<sup>35</sup> with appropriate device geometry simulates the band profile and currents in PG-FET. Solution of the three-dimensional Poisson equation captures the effect of contact dimensions, and the drift-diffusion equation describes onedimensional carrier transport along the CNT. Analytical expressions for field-dependent mobility<sup>25,35,36</sup> and carrier densities are calibrated from independent experiments,<sup>37–39</sup> and CNTs are doped with acceptors to capture the influence of (oxygen- and water-induced) negatively charged interface defects.<sup>40,41</sup> We also use extensively and independently calibrated models for

VOL.7 • NO.2 • 1299–1308 • 2013

JAI

ARTICLE

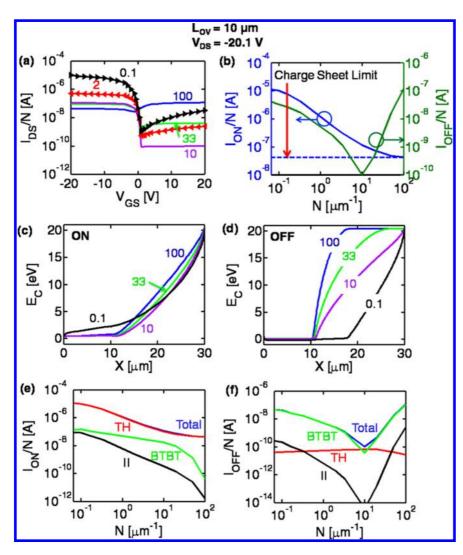

Figure 2. (a)  $I_{DS}-V_{GS}$  characteristics of PG-FET suggest strong dependence on *N*. (b) Plot of  $I_{DS}$  per CNT from such characteristics at  $V_{GS} = -20$  V ( $I_{ON}/N$ ) and  $V_{GS} = 20$  V ( $I_{OFF}/N$ ) as a function of *N*. A unique feature of V-shaped  $I_{OFF}/N$  vs *N* relationship is only expected from 3D electrostatic simulation of PG-FET. A dotted line drawn is the  $I_{ON}/N$  at charge-sheet limit (maximum attainable CNT density: ~574 CNTs of diameter 1.74 nm in 1  $\mu$ m width) condition. (c,d) Conduction band profiles for different *N* in ON and OFF states. (e)  $I_{ON}/N$  for any *N* is dominated by the thermionic injection of carriers (TH) over the hole-energy barrier near the source contact and subsequent drift of hole through CNTs. (f) In OFF state, BTBT is the dominant current component. The schematic band diagrams are shown in Supporting Information Figure 1a,b corresponding to low-density and high-density CNTs in order to explain different leakage current components in the OFF state.

the probability of band-to-band tunneling<sup>17,20,42</sup> (BTBT) and impact ionization<sup>42</sup> (II) at location *x* along the CNT using  $\sim \exp[-E_{C,BTBT(II)}/(dV/dx)]$ ,<sup>42</sup> where |dV/dx| is the electric field along the channel direction and  $E_{C,BTBT(II)} \sim 1/d^2$  is the critical field for BTBT (II). See Methods section for modeling details.

Figure 2a shows drain current ( $I_{DS}$ ) versus gate voltage ( $V_{GS}$ ) characteristics of a PG-FET for a broad range of  $N \sim 0.067-100$  CNTs/ $\mu$ m (with  $L_{OV} = 10 \mu$ m, channel length  $L = L_{OV} + L_{UN} = 30 \mu$ m,  $L_{S/D} = 2 \mu$ m, oxide thickness  $T_{OX} = 400$  nm, source/drain contact thickness  $T_{S/D} = 40$  nm, gate contact thickness  $T_G = 200$  nm, and substrate thickness,  $T_{SUB} = 6 \mu$ m) operated at high source–drain bias,  $V_{DS} = -20.1$  V. The I-V characteristics at all densities show features of ambipolar transport. The decrease of ON current (*i.e.*,  $I_{DS}$

at  $V_{GS} = -20$  V) per CNT ( $I_{ON}/N$ ) in Figure 2b is expected using the classical drain current and oxide capacitance expressions of  $I_{\rm DS} \sim C_{\rm OX} (V_{\rm GS} - V_{\rm T}) V_{\rm DS}$  and  $C_{OX} = 2\pi\varepsilon_0\varepsilon_{OX}N/\ln[\sinh(\pi(2T_{OX} + d/2)N)/\sinh(\pi dN/dN/dN))$ 2)],<sup>4,23,43</sup> where  $\varepsilon_0$  is the free space permittivity and  $\varepsilon_{OX}$  is the dielectric constant of the gate oxide. Analytically calculated I<sub>DS</sub>/N follows simulation (not shown), with differences that can be attributed to the full-gate and partial-gate geometries used for analytical and simulation approaches, respectively. To calculate the highest density (i.e., charge sheet) limit of ON current, let us consider a tightly packed array with CNT spacing equal to the diameter of the tube ( $\sim$ 1.74 nm), with corresponding density of  $\sim$ 574 CNTs/ $\mu$ m. We simulate the device for this CNT density and find that, in this highest density limit, the ON state current per CNT is

VOL.7 • NO.2 • 1299-1308 • 2013

JAI

ARTICLE

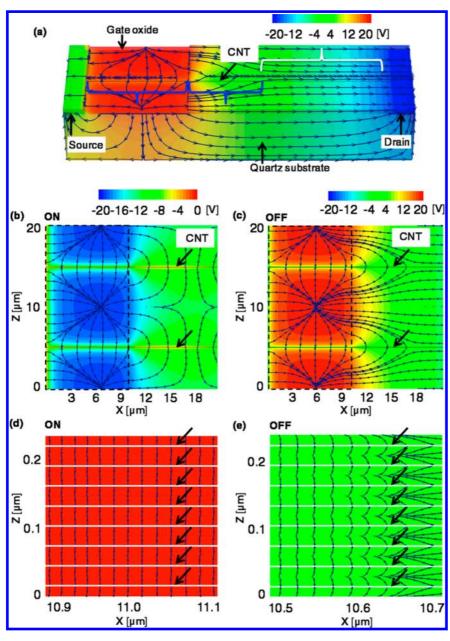

Figure 3. (a) Three-dimensional electric field lines (tangential to the surface) for PG-FET having  $N = 0.1 \text{ CNTs}/\mu m$  in the OFF state. The left blue bracket covering the 10  $\mu m$  gate length, together with the right blue, shows the region where electric field lines from the wings of the gate are terminating in the nanotube. Electric field lines under the white bracket prefer to terminate in the drain. (b,c) XZ cuts through the array of CNTs in the PG-FET of panel a for ON and OFF states. (d,e) Similar XZ cuts for PG-FET having N = 33 CNTs/ $\mu m$ .

~4.25 × 10<sup>-8</sup> A, that is, 24.4  $\mu$ A/ $\mu$ m (see Figure 2b). This numerical result is within a factor of 2 of the current density obtained from a simple 2D charge-sheet calculation based on  $I_{DS}/N = 1/2\mu_{avg}(\varepsilon_0\varepsilon_{OX}/T_{OX})(d/L)(V_{GS} - V_T)^2$ , suggesting the validity of our numerical simulation. The profiles of the conduction band (Figure 2c) in the ON state under the gate show higher pull-up (stronger channel inversion) of the barrier for smaller *N* and result in higher  $I_{ON}$ . Figure 2e shows that thermionic (TH) injection of carriers over the hole-energy barrier near the source contact (injected carriers drift through the CNT) is the dominant current component in the ON state. The OFF current ( $I_{DS}$  at  $V_{GS} = 20$  V) per CNT ( $I_{OFF}/N$ ) has V-shaped turn-around (Figure 2b): it first decreases as  $I_{OFF}/N \sim N^{-1}$  for N = 0.067 - 10 CNTs/ $\mu$ m and then increases as  $I_{OFF}/N \sim N^3$ , for N = 10 - 100 CNTs/ $\mu$ m. The remarkable feature of  $I_{OFF}$  is unexpected from classical 2D electrostatics that would suggest a monotonous decrease in  $I_{OFF}$  with N (like the  $I_{ON}$  vs N relationship discussed above). The conduction band diagram shown in Figure 2d offers a clue regarding this non-intuitive V-shaped turn-around of  $I_{OFF}$  as a function of N. For same  $L_{OV}$ , PG-FET with  $N \sim 100$  CNTs/ $\mu$ m has a rapid potential drop near the beginning of underlap region—analogous to the thin-film limit related to 2D

VOL.7 • NO.2 • 1299-1308 • 2013

IAI

ARTICLE

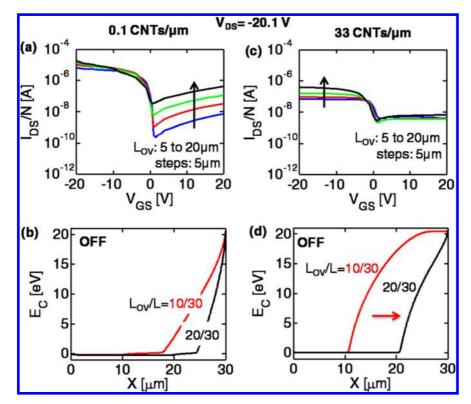

Figure 4. Simulated  $I_{DS}-V_{GS}$  characteristics for different  $L_{OV}$  in PG-FETs with (a)  $N = 0.1 \text{ CNTs}/\mu m$ , (c)  $N = 33 \text{ CNTs}/\mu m$ . Conduction band profiles for different  $L_{OV}$  in the OFF state of PG-FETs with (b)  $N = 0.1 \text{ CNTs}/\mu m$ , (d)  $N = 33 \text{ CNTs}/\mu m$ .

electrostatics.<sup>44,45</sup> Resultant high electric field (>40 kV/cm) in that region induces high BTBT (Figure 2f) and hence large  $l_{OFF}$ . As N is decreased, the gate parasitically controls CNTs in the underlap region and reduces band bending and electric field, and hence BTBT and  $l_{OFF}$  (Figure 2f). Beyond the inflection point at  $N \sim 10 \text{ CNTs}/\mu\text{m}$ , parasitic effect reduces band bending near the beginning of the underlap region, but increases band bending (and electric field) near the drain contact. This leads to increase BTBT and, therefore,  $l_{OFF}$  (Figure 2f).

In order to understand the extent of parasitic gate coupling in the underlap region, we explore the field profiles in PG-FET as obtained from 3D simulation and comment on the dimensionality of CNTs in PG-FET configurations. Figure 3a plots the 3D electric field (tangential component to the surface) for a PG-FET with N = 0.1 CNTs/ $\mu$ m biased in the OFF state with  $V_{GS} =$ 20 V and  $V_{DS} = -20.1$  V. The field lines originate at the gate and terminate at the CNT and at the source and drain contacts. The crucial role of finite density of states for a 1D CNT is obvious from the field profile: the field lines from the 3D gate and drain must travel along the channel through the quartz substrate before they can terminate onto the nanotube. Of the 3D field profile, a 2D cut in the XZ plane through the CNT highlights the salient features. Figure 3b,c plots such a 2D cut of the field profile in ON and OFF states, respectively, for N = 0.1 CNTs/ $\mu$ m. Though the field line directions are opposite in ON and OFF states due to the opposite gate biases, the virtual extended gate length (the underlap region of CNT over which the gate has direct control) remains the same in both cases. The field lines from the gate control CNT are  $\sim 8 \,\mu$ m in the underlap region for substantial decay of the field, while the rest of the gate field lines couple directly to the drain contact, thereby explaining the gradual drop of potential in the underlap region at the lower density limit in Figure 2d. This emergence of the virtual gate (beyond the geometric edge of the real gate) through parasitic coupling of the 2D gate to the 1D CNT creates the nontrivial variation in potential profile (and  $I_{OFF}/N$ ) as a function of N in Figure 2. The field lines from the gate of a PG-FET with high density of CNTs (N = 33 CNTs/ $\mu$ m for Figure 3d,e) terminate within a very short distance (~0.7-1  $\mu$ m) in the underlap region, while the rest of the underlap region is controlled by the drain as an equipotential region. Such equipotential region in the underlap results from the p-type doping of CNTs due to interface defects; this region behaves like an implicit drain contact and explains the characteristic shape of potential drop along the CNT in Figure 2d.

The extents of parasitic gate control in PG-FETs with low- and high-density CNTs are also evident when  $L_{\rm OV}$ is varied, while keeping *L* and  $T_{\rm OX}$  fixed. For PG-FET with  $N \sim 0.1$  CNTs/ $\mu$ m, an increase in  $L_{\rm OV}$  increases  $I_{\rm OFF}$  by orders of magnitude, while keeping the variation in  $I_{\rm ON}$ relatively small (Figure 4a). Higher  $L_{\rm OV}$  brings a larger part of the CNT under gate control and causes linear

VOL.7 • NO.2 • 1299-1308 • 2013

A

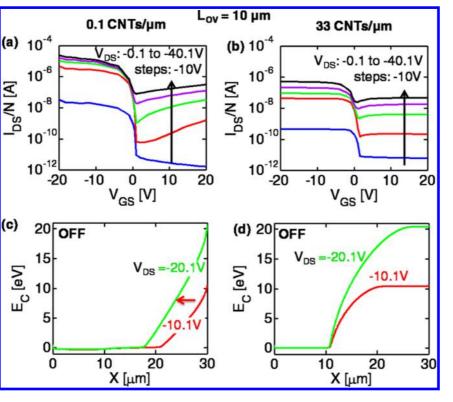

Figure 5. Simulated  $I_{DS}-V_{GS}$  characteristics for different  $V_{DS}$  in PG-FETs with (a) N = 0.1 CNTs/ $\mu$ m, (b) N = 33 CNTs/ $\mu$ m. Conduction band profiles for different  $V_{DS}$  in the OFF state of PG-FETs with (c) N = 0.1 CNTs/ $\mu$ m, (d) N = 33 CNTs/ $\mu$ m.

increase in  $I_{ON}$  with  $L_{OV}$ . Exponential increase in  $I_{OFF}$  with  $L_{OV}$  arises from the increase in band bending (*i.e.*, electric field) in the underlap region near the drain (Figure 4b). Since the BTBT component of  $I_{OFF}$  depends exponentially on the electric field, a linear increase in electric field with  $L_{OV}$  causes exponential increase in  $I_{OFF}$ . On the other hand, for PG-FET with N = 33 CNTs/ $\mu$ m, parasitic gate control is less prominent and consequently the effect of  $L_{OV}$  variation is less dramatic (Figure 4c). The only increase in  $I_{ON}$  with  $L_{OV}$  results from the increase in electrostatic control in a greater portion of the CNT. Electric field ( $\equiv$ derivative of band profiles in Figure 4d) in the underlap region with variation in  $L_{OV}$ , however, remains essentially similar; therefore, the  $I_{OFF}$  is unchanged.

We finally discuss the extent of parasitic gate control as a function of drain bias for PG-FETs having different CNT densities. Figure 5a (for N = 0.1 CNTs/ $\mu$ m) and 5b (for N = 33 CNTs/ $\mu$ m) show higher increase in  $I_{ON}/N$  as  $V_{DS}$  changes from -0.1 to -10.1 V compared to the increase in  $I_{ON}/N$  for  $V_{DS} < -10.1$  V. The presence of hole fluxes both in the drain and in the source sides at smaller  $|V_{DS}|$  and the disappearance of the ones in the drain side at larger  $|V_{DS}|$  are the reasons for such  $I_{ON}/N$  variation.  $I_{OFF}$ , on the other hand, is controlled by electric field in the underlap region primarily through BTBT (Figure 2f); therefore,  $I_{OFF}$  increases in band bending (Figure 5c,d).

**Experimental Validation.** The three key theoretical predictions of parasitic gate coupling (*i.e.*, *L*<sub>OV</sub> dependence

of  $I_{OFF}/N$  in Figure 4,  $V_{DS}$  dependence of  $I_{ON}/N$  in Figure 5, and high OFF currents in Figure 5) in PG-FETs with low CNT density are explored using a series of experiments on PG-FETs with a single semiconducting CNT as the channel material. The low-density limit offers the most stringent test of the predictions of the model because the parasitic 3D-to-1D coupling is most pronounced for low tube densities.

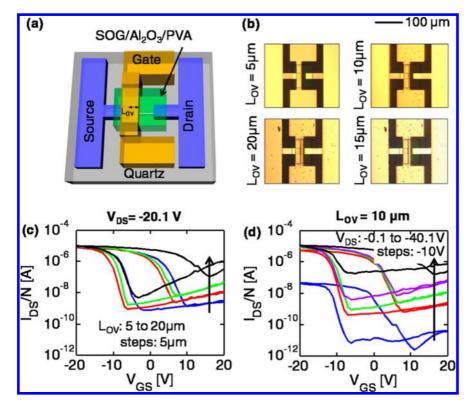

Fabrication of such PG-FET (Schematic in Figure 6a) starts with the deposition of parallel stripes of iron (0.6 nm) as the catalyst on ST-cut quartz substrates, followed by CVD growth of single-wall aligned-array low-density (0.1–0.2 CNTs/µm) CNTs.<sup>4,46</sup> After photolithographic definition of source and drain electrodes (with  $L \sim 30 \ \mu m$  separation) via e-beam evaporation (Ti/Pd (2 nm/40 nm)) and lift-off, CNTs except those in narrow strips ( $\sim$ 3  $\mu$ m width) are completely removed by reactive ion etching (RIE). Single CNT devices are screened via SEM (and/or AFM) among devices with small numbers of CNTs, and the diameter of the CNT in the channel is determined by the analysis of Raman spectroscopy. After triple layers of gate dielectric (SOG/ Al<sub>2</sub>O<sub>3</sub>/cross-linked PVA with effective oxide thickness (EOT) of 400 nm) are deposited on CNTs, Ti gate metal (50 nm) is photolithographically defined with a gate overlap  $L_{OV} = 5 \,\mu m$  by e-beam evaporation and lift-off. Finally, CNTs with semiconducting properties are confirmed by electrical measurements. After all electrical measurements for different  $V_{DS}$  are completed in vacuum (pressure =  $1 \times 10^{-4}$  Torr and temperature = 60 °C) in

VOL.7 • NO.2 • 1299-1308 • 2013

JAI

Figure 6. (a) Schematic of experimental structure of partial-gate CNTFET (PG-FET) with single semiconducting CNT (corresponding to  $N \le 0.1$  CNTs/ $\mu$ m limit) as the channel, (b) optical images for PG-FET with gradually increasing gate overlap from 5 to 20  $\mu$ m. Experimental  $I_{DS}-V_{GS}$  characteristics in PG-FETs with N = 0.1 CNTs/ $\mu$ m for (c)  $V_{DS} = -20.1$  V, (d)  $L_{OV} = 10 \ \mu$ m.

order to avoid electrical breakdown of the CNT,<sup>47</sup> gate overlap ( $L_{OV}$ ) for the same CNT PG-FET is extended *via* the same method above, followed by the same electrical characterization for each  $L_{OV}$  condition (Figure 6b shows optical micrograph of a PG-FET with different  $L_{OV}$ ). In the experimental structure, the source, drain, and gate contact widths are such that we can assume  $W_{G,S,D} \sim 30 \,\mu\text{m}$ . Indeed for  $W_{G,S,D} > 10 \,\mu\text{m}$ , devices show negligible width dependency and currents,  $I_{DS}/N$ , saturate (Figure 2b). In this study, the diameter of the semiconducting CNT is estimated as  $d \sim 1.67$  nm from G-band Raman spectra (Supporting Information Figure 2), and the illustration of the experimental procedures is provided through the schematic diagram in Supporting Information Figure 5.

Figure 6c plots the measured  $I_{DS}-V_{GS}$  characteristics during a  $V_{GS} = -20$  to 20 V sweep for PG-FETs with different  $L_{OV}$  at fixed  $V_{DS}$ , while Figure 6d plots the same measured at different  $V_{DS}$  with fixed  $L_{OV}$ . Measurements are remarkably similar to the simulation results obtained for PG-FETs with low-density CNTs (Figures 4a and 5a). ( $N \sim 0.1$  CNTs/ $\mu$ m is a good approximation to simulate single CNT PG-FET, as the current for N < 0.1 CNTs/ $\mu$ m saturates in Figure 2b.) The only differences in terms of higher threshold voltage and larger subthreshold slope in the experiment reflect the omission of trapping–detrapping dynamics of interface and bulk defects<sup>29</sup> during simulation.

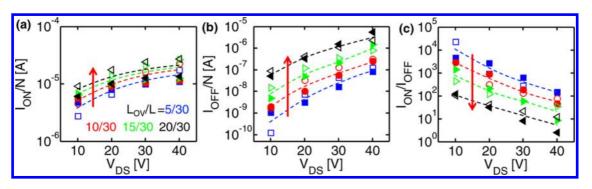

The synopsis of the key features ( $I_{ON}$ ,  $I_{OFF}$ , and  $I_{ON}/I_{OFF}$ ) of measured  $I_{DS} - V_{GS}$  characteristics is provided in Figure 7

for PG-FETs fabricated with various levels of  $L_{OV}$ . At fixed  $L_{OV}$ , an increase in  $V_{DS}$  increases both  $I_{ON}$  (Figure 7a) and  $I_{OFF}$  (Figure 7b) because of the increase in the electric field along the CNT. Variation in  $L_{OV}$  also produces expected linear variation in  $I_{ON}$  (Figure 7a) and exponential variation in  $I_{OFF}$  (Figure 7b) and, therefore, a decrease in  $I_{ON}/I_{OFF}$  at higher  $V_{DS}$  and higher  $L_{OV}$  (Figure 7c), as expected for PG-FETs with large contact widths. Simulation of PG-FET based on the model discussed above confirms the experimental trend.

Parametric Dependence of Electrostatic Coupling. The remarkably complex interplay between the 3D electric field and the 1D CNT discussed above cannot be described by simplified numerical or analytical models. To check for the universality/robustness of our results, we vary gate oxide thickness  $(T_{OX})$  and dielectric constant ( $\varepsilon_{OX}$ ) and CNT diameter (d), and the results are summarized in Supporting Information Figures 6-11 and Supporting section 2. Although the  $I_{DS} - V_{GS}$  characteristics change slightly as a function of device parameters, as long as a reasonably thick dielectric (such as quartz) is used as substrate for the CNT device, our results demonstrate that the gate channel parasitic coupling remains an important concern. This 3D capacitive coupling can be suppressed by using full-gate covering the entire channel. Even for partial gates, the coupling can be reduced by decreasing the gate width; see Supporting Information Figures 12 and 13. The gradual suppression of parasitic lines is obvious, especially at

VOL.7 • NO.2 • 1299-1308 • 2013

JAN

Figure 7. Simulated (open symbol) and experimental (solid symbol) (a)  $I_{ON}/N$  (at  $V_{GS} = -20$  V) vs  $V_{DS}$ , (b)  $I_{OFF}/N$  (at  $V_{GS} = 20$  V) vs  $V_{DS}$ , and (c)  $I_{ON}/I_{OFF}$  vs  $V_{DS}$ , as obtained from Figures 4–6.

0.1  $\mu$ m gate width, because the parasitic field lines originating at the wings of the wider gate are now absent. This offers us an opportunity to work with partial-gated test structures whose results can be interpreted by simple classical models uncorrupted by fringing effects.

## CONCLUSION

In summary, we have used a three-dimensional selfconsistent model for partial-gate CNTFETs to demonstrate a surprisingly complex electrostatic interaction between 3D electric field and 1D NTs/NWs. Our results show the following results. (1) The parasitic coupling is most significant at low NT/NW densities, especially in the limit of electrostatically doped, single NT/NW devices. (2) Although the coupling is suppressed with increasing NT/NW densities, a V-shaped turn-around in the OFF current (Figure 2b) reflects the importance of

#### **METHODS**

**Modeling Details.** The simulation model for PG-FET selfconsistently solves the electrostatics and charge density. To model electrostatics potential with the effect of contact dimension, we solve 3D Poisson equation

$$\nabla(\varepsilon\nabla V) = -\rho \tag{1}$$

Here, *V* is the spatial-dependent electrostatics potential and  $\varepsilon$  is the material-dependent permittivity. Charge density is  $\rho = q(p - n - N_a)$ , where *q* is the electron charge. Poisson equation is linked with continuity and drift-diffusion through hole and electron concentrations, *p* and *n*. The effect of negatively charged interfacial trap,<sup>40,41</sup> because of the inevitable presence of oxygen and water molecules on the surface of the CNTs, is represented through ionized impurity concentration  $N_a^-$ .

To obtain charge density, the following continuity equations are solved:

$$\frac{1}{q}\frac{dI_{n}}{dx} - R + G_{BBT, n} + G_{Il, n} + G_{SBT, n} = 0; \frac{1}{q}\frac{dI_{p}}{dx} + R - G_{BBT, p}$$

$$- G_{Il, p} - G_{SBT, p} = 0$$

(2)

where  $R = \beta(np - n_i^2)$  is the radiative rate for direct band-toband recombination, <sup>35,48,49</sup>  $\beta$  is the recombination coefficient, and  $n_i$  is the intrinsic carrier concentration of the CNT. Band-toband tunneling, impact ionization, and Schottky barrier tunneling are represented as the generation in the CNT channel through the terms  $G_{\text{BTBT},n(p)}$ ,  $G_{\text{II},n(p)}$ , and  $G_{\text{SBT},n(p)}$ , respectively, 3D electrostatic coupling even at moderate NT/NW densities. (3) Since the substrate always offers a pathway for the 3D gate fields to terminate onto the 1D channel (Figure 1b) therefore, the parasitic coupling persists despite scaling of gate oxide thickness, increase in dielectric constant, and reduction of diameter of the NTs/NWs. (4) The OFF current is dominated by BTBT tunneling. At low NT/NW densities,  $I_{OFF}$  depends exponentially on overlap length, suggesting the importance of parasitic coupling. (5) The asymptotic charge-sheet limit is reached for partial gate devices at relatively high densities (>100 CNTs/ $\mu$ m).

The complexity of electrostatic interaction suggests a careful reconsideration of carrier transport in electrostatically doped diodes, tunnel FET, various other characterization/test structures, *etc.*, widely used for parameter extraction and technology development of CNT-based nano- and optoelectronics.

for electron (hole). The expressions for  $G_{BTBT,n(p),}^{17,20,42,50}$  $G_{II,n(p),}^{42}$  and  $G_{SBT,n(p)'}^{35,51,52}$  along the channel region are

$$G_{\text{BTBT, n(p)}}(x) = \frac{5}{9} \frac{|dV/dx|^2 td}{\pi \hbar^2 v_F} \exp\left[-\frac{E_G^2}{\delta \hbar v_F |dV/dx|}\right]$$

(3)

$$G_{\rm Il_{r}\,n(p)}(x) = \frac{5 \times 10^{3} I_{\rm S}}{q} \exp\left[-\frac{3 E_{\rm G}}{23.33 |{\rm d}V/{\rm d}x|d}\right] \tag{4}$$

G<sub>SBT</sub>, n(p)

$$= \frac{\pi \left| \frac{\mathrm{d}V}{\mathrm{d}x} \right| A T t d}{k_{\mathrm{B}}} \left[ \exp \left[ -\frac{2\sqrt{2m}}{\hbar} \int_{0}^{x} \sqrt{E_{\mathrm{rx},\mathrm{C(V)}}} \mathrm{d}r \right] \ln \left[ \frac{1 + \exp\eta_{\mathrm{n(p)}}}{1 + \exp\eta_{\mathrm{n(p)},\mathrm{S}}} \right] + \exp \left[ -\frac{2\sqrt{2m}}{\hbar} \int_{x}^{L} \sqrt{E_{\mathrm{rx},\mathrm{C(V)}}} \mathrm{d}r \right] \ln \left[ \frac{1 + \exp\eta_{\mathrm{n(p)}}}{1 + \exp\eta_{\mathrm{n(p)},\mathrm{D}}} \right] \right]$$

(5)

Here,  $\hbar$  is the reduced Planck's constant, *t* is the wall thickness of the CNT, and |dV/dx| is the electric field along the channel direction. The Fermi velocity ( $v_{\rm F} \sim 10^8$  cm/s) is a characteristic of the band structure of the SWNTs.<sup>17</sup> The band gap of CNTs is related to the diameter of the tubes,  $E_{\rm G} = 0.7/d$  eV,<sup>20</sup> so that BTBT generation is more pronounced in larger diameter CNTs, as expected. The ideality factor,  $\delta \sim 8.34$ , within

the exponential function in eq 3 is used to match the theoretical results to the experiments (Figure 4 in the Supporting Information). It is noticeable that a simple analytical model uses a somewhat lower value of  $\delta \sim 2.78^{20,42}$  From eq 5,  $\eta_{n,S(D)} = (E_{F,S(D)} - E_C)/k_BT$ ,  $\eta_{p,S(D)} = (E_V - E_{F,S(D)})/k_BT$ ,  $E_{rx,C} = E_C(r) - E_C(x)$ ,  $E_{rx,V} = E_V(x) - E_V(r)$ , and r is a position variable along the channel. Effective mass of lectron and hole is  $m = E_G m_0/20$ , where  $m_0$  is the mass of free carrier,  $E_{F,S(D)}$  is the Fermi energy for carriers in S(D) contact,  $A = 1.5 \times 10^2 E_G A/cm^2/K^2$  is the Richardson constant,  $k_B$  is the Boltzmann constant, and T is the lattice temperature.

The  $l_{\rm S}$  used in the prefactor of the impact ionization generation is the summation of all other current components (flow of the carriers may induce impact ionization depending on band bending magnitude and direction). In order for band-toband tunneling to take place, the band potential must bend above  $E_{\rm G}/q$ . The drift-diffusion current for electron (hole)  $l_{\rm n(p)}$  in eq 2 is represented as

$$I_{n}=-qn\mu_{\text{FE}}\,\frac{dV}{dx}+qD_{n}\frac{dn}{dx};\ I_{p}=-qp\mu_{\text{FE}}\,\frac{dV}{dx}-qD_{p}\,\frac{dp}{dx}\quad\text{(6)}$$

Here, the field-dependent mobility  $\mu_{\rm FE}$  is a function of CNT diameter, <sup>25,35,36</sup> and  $D_{\rm n(p)}$  is the diffusion coefficient of the electron (hole). The expressions  $\mu_{\rm FE}$  and  $D_{\rm n(p)}$  are provided in Supporting Information. Supporting Information Figure 3 sketches out the flow chart for simulation. The simulation procedures are explained in detail in the Supporting Information section 1.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. The work was funded by Materials Structures and Devices Focus Center (Task ID: 2051.003.4) of Semiconductor Research Corporation. Devices were simulated using computational support from Network of Computational Nanotechnology at Purdue University.

*Supporting Information Available*: Measurement and simulation procedures for 3D-CNTFETs. This material is available free of charge *via* the Internet at http://pubs.acs.org.

#### **REFERENCES AND NOTES**

- Dresselhaus, M. S.; Lin, Y. M.; Rabin, O.; Jorio, A.; Souza Filho, A. G.; Pimenta, M. A.; Saito, R.; Samsonidze, G.; Dresselhaus, G. Nanowires and Nanotubes. *Mater. Sci. Eng., C* 2003, 23, 129–140.

- Law, M.; Goldberger, J.; Yang, P. Semiconductor Nanowires and Nanotubes. Annu. Rev. Mater. Res. 2004, 34, 83–122.

- Xia, Y.; Yang, P.; Sun, Y.; Wu, Y.; Mayers, B.; Gates, B.; Yin, Y.; Kim, F.; Yan, H.One-Dimensional Nanostructures: Synthesis, Characterization, and Applications. *Adv. Mater.* 2003, *15*, 353–389.

- Kang, S. J.; Kocabas, C.; Ozel, T.; Shim, M.; Pimparkar, N.; Alam, M. A.; Rotkin, S. V; Rogers, J. A. High-Performance Electronics Using Dense, Perfectly Aligned Arrays of Single-Walled Carbon Nanotubes. *Nat. Nanotechnol.* **2007**, *2*, 230–236.

- Koswatta, S. O.; Valdes-Garcia, A.; Steiner, M. B.; Lin, Y.-M.; Avouris, P. Ultimate RF Performance Potential of Carbon Electronics. *IEEE Trans. Microwave Theory Tech.* 2011, *59*, 2739–2750.

- Ryu, K.; Badmaev, A.; Wang, C.; Lin, A.; Patil, N.; Gomez, L.; Kumar, A.; Mitra, S.; Wong, H.-S. P.; Zhou, C. CMOS-Analogous Wafer-Scale Nanotube-on-Insulator Approach for Submicrometer Devices and Integrated Circuits Using Aligned Nanotubes. *Nano Lett.* **2009**, *9*, 189–197.

- Kocabas, C.; Pimparkar, N.; Yesilyurt, O.; Kang, S. J.; Alam, M. A.; Rogers, J. A. Experimental and Theoretical Studies of Transport through Large Scale, Partially Aligned Arrays of Single-Walled Carbon Nanotubes in Thin Film Type Transistors. *Nano Lett.* 2007, *7*, 1195–1202.

- Li, Y.; Qian, F.; Xiang, J.; Lieber, C. M. Nanowire Electronic and Optoelectronic Devices. *Mater. Today* 2006, *9*, 18–27.

- Xiong, F.; Liao, A. D.; Estrada, D.; Pop, E. Low-Power Switching of Phase-Change Materials with Carbon Nanotube Electrodes. *Science* 2011, *332*, 568–570.

- Lee, S.-H.; Jung, Y.; Agarwal, R. Highly Scalable Non-volatile and Ultra-Low-Power Phase-Change Nanowire Memory. *Nat. Nanotechnol.* 2007, 2, 626–630.

- Opatkiewicz, J.; Lemieux, M. C.; Bao, Z. Nanotubes on Display: How Carbon Nanotubes Can Be Integrated into Electronic Displays. ACS Nano 2010, 4, 2975–2978.

- Sun, X. W.; Wang, J. X. Fast Switching Electrochromic Display Using a Viologen-Modified ZnO Nanowire Array Electrode. *Nano Lett.* **2008**, *8*, 1884–1889.

- Gabor, N. M.; Zhong, Z.; Bosnick, K.; Park, J.; McEuen, P. L. Extremely Efficient Multiple Electron—Hole Pair Generation in Carbon Nanotube Photodiodes. *Science* 2009, 325, 1367–1371.

- Mueller, T.; Kinoshita, M.; Steiner, M.; Perebeinos, V.; Bol, A. A.; Farmer, D. B.; Avouris, P. Efficient Narrow-Band Light Emission from a Single Carbon Nanotube P–N Diode. *Nat. Nanotechnol.* **2010**, *5*, 27–31.

- Kim, S. N.; Rusling, J. F.; Papadimitrakopoulos, F. Carbon Nanotubes for Electronic and Electrochemical Detection of Biomolecules. *Adv. Mater.* 2007, *19*, 3214–3228.

- Nair, P. R.; Alam, M. A. Design Considerations of Silicon Nanowire Biosensors. *IEEE Trans. Electron Devices* 2007, 54, 3400–3408.

- Jena, D.; Fang, T.; Zhang, Q.; Xing, H. Zener Tunneling in Semiconducting Nanotube and Graphene Nanoribbon P–N Junctions. *Appl. Phys. Lett.* **2008**, *93*, 112106.

- Gruner, G. Carbon Nanotube Transistors for Biosensing Applications. Proc. SPIE 2005, 5592, 175–182.

- Franklin, A. D.; Chen, Z. Length Scaling of Carbon Nanotube Transistors. *Nat. Nanotechnol.* 2010, *5*, 858–862.

- Bosnick, K.; Gabor, N.; McEuen, P. Transport in Carbon Nanotube P-I-N Diodes. Appl. Phys. Lett. 2006, 89, 163121.

- Liu, C.-H.; Wu, C.-C.; Zhong, Z. A Fully Tunable Single-Walled Carbon Nanotube Diode. *Nano Lett.* 2011, *11*, 1782–1785.

- Guo, J.; Goasguen, S.; Lundstrom, M.; Datta, S. Metal– Insulator–Semiconductor Electrostatics of Carbon Nanotubes. *Appl. Phys. Lett.* 2002, *81*, 1486–1488.

- Cao, Q.; Xia, M.; Kocabas, C.; Shim, M.; Rogers, J. A.; Rotkin, S. V. Gate Capacitance Coupling of Singled-Walled Carbon Nanotube Thin-Film Transistors. *Appl. Phys. Lett.* 2007, 90, 023516.

- 24. Nair, P. R.; Alam, M. A. Performance Limits of Nanobiosensors. *Appl. Phys. Lett.* **2006**, *88*, 233120.

- Zhou, X.; Park, J.-Y.; Huang, S.; Liu, J.; McEuen, P. Band Structure, Phonon Scattering, and the Performance Limit of Single-Walled Carbon Nanotube Transistors. *Phys. Rev. Lett.* 2005, *95*, 146805.

- Estrada, D.; Dutta, S.; Liao, A.; Pop, E. Reduction of Hysteresis for Carbon Nanotube Mobility Measurements Using Pulsed Characterization. *Nanotechnology* **2010**, *21*, 85702.

- Kumar, S.; Pimparkar, N.; Murthy, J. Y.; Alam, M. A. Self-Consistent Electrothermal Analysis of Nanotube Network Transistors. J. Appl. Phys. 2011, 109, 014315.

- Pimparkar, N.; Alam, M. A. A "Bottom-Up" Redefinition for Mobility and the Effect of Poor Tube – Tube Contact on the Performance of CNT Nanonet Thin-Film Transistors. *IEEE Electron Device Lett.* **2008**, *29*, 1037–1039.

- Jin, S. H.; Islam, A. E.; Kim, T.; Kim, J.; Alam, M. A.; Rogers, J. A. Sources of Hysteresis in Carbon Nanotube Field-Effect Transistors and Their Elimination *via* Methylsiloxane Encapsulants and Optimized Growth Procedures. *Adv. Funct. Mater.* 2012, *22*, 2276–2284.

- Alam, K.; Lake, R. Performance of 2 nm Gate Length Carbon Nanotube Field-Effect Transistors with Source/Drain Underlaps. *Appl. Phys. Lett.* 2005, *87*, 073104.

- Heinze, S.; Tersoff, J.; Avouris, P. Electrostatic Engineering of Nanotube Transistors for Improved Performance. *Appl. Phys. Lett.* 2003, *83*, 5038–5040.

- Lin, Y.-M.; Appenzeller, J.; Avouris, P. Ambipolar-to-Unipolar Conversion of Carbon Nanotube Transistors by Gate Structure Engineering. *Nano Lett.* 2004, *4*, 947–950.

- Fiori, G.; lannaccone, G.; Klimeck, G. A Three-Dimensional Simulation Study of the Performance of Carbon Nanotube

Field-Effect Transistors with Doped Reservoirs and Realistic Geometry. *IEEE Trans. Electron Devices* **2006**, *53*, 1782–1788.

- Neophytou, N.; Lundstrom, M. S. Three-Dimensional Electrostatic Effects of Carbon Nanotube Transistors. *IEEE Trans. Nanotechnol.* 2006, *5*, 385–392.

- Xie, X.; Islam, A. E.; Wahab, M. A.; Ye, L.; Ho, X.; Alam, M. A.; Rogers, J. A. Electroluminescence in Aligned Arrays of Single-Wall Carbon Nanotubes with Asymmetric Contacts. *ACS Nano* 2012, *6*, 7981–7988.

- Perebeinos, V.; Tersoff, J.; Avouris, P. Electron–Phonon Interaction and Transport in Semiconducting Carbon Nanotubes. *Phys. Rev. Lett.* 2005, *94*, 086802.

- Liang, J.; Akinwande, D.; Wong, H.-S. P. Carrier Density and Quantum Capacitance for Semiconducting Carbon Nanotubes. J. Appl. Phys. 2008, 104, 064515.

- Akinwande, D.; Nishi, Y.; Wong, H.-S. P. An Analytical Derivation of the Density of States, Effective Mass, and Carrier Density for Achiral Carbon Nanotubes. *IEEE Trans. Electron Devices* 2008, *55*, 289–297.

- Marulanda, J. M.; Srivastava, A. Carrier Density and Effective Mass Calculations in Carbon Nanotubes. *Phys. Status Solidi B* **2008**, *245*, 2558–2562.

- Aguirre, C. M.; Levesque, P. L.; Paillet, M.; Lapointe, F.; St. Antoine, B. C.; Desjardins, P.; Martel, R. The Role of the Oxygen/Water Redox Couple in Suppressing Electron Conduction in Field-Effect Transistors. *Adv. Mater.* 2009, *21*, 3087–3091.

- Kim, W.; Javey, A.; Vermesh, O.; Wang, Q.; Li, Y.; Dai, H. Hysteresis Caused by Water Molecules in Carbon Nanotube Field-Effect Transistors. *Nano Lett.* **2003**, *3*, 193–198.

- 42. Liao, A.; Zhao, Y.; Pop, E. Avalanche-Induced Current Enhancement in Semiconducting Carbon Nanotubes. *Phys. Rev. Lett.* **2008**, *101*, 256804.

- Balci, O.; Kocabas, C. High Frequency Performance of Individual and Arrays of Single-Walled Carbon Nanotubes. *Nanotechnology* 2012, 23, 245202.

- Knoch, J.; Appenzeller, J. Tunneling Phenomena in Carbon Nanotube Field-Effect Transistors. *Phys. Status Solidi A* 2008, 205, 679–694.

- 45. Yan, R.-H.; Ourmazd, A.; Lee, K. F. Scaling the Si MOSFET: From Bulk to SOI to Bulk. *IEEE Trans. Electron Devices* **1992**, *39*, 1704–1710.

- Xiao, J.; Dunham, S.; Liu, P.; Zhang, Y.; Kocabas, C.; Moh, L.; Huang, Y.; Hwang, K.-C.; Lu, C.; Huang, W.; et al. Alignment Controlled Growth of Single-Walled Carbon Nanotubes on Quartz Substrates. *Nano Lett.* **2009**, *9*, 4311–4319.

- Liao, A.; Alizadegan, R.; Ong, Z.-Y.; Dutta, S.; Xiong, F.; Hsia, K.; Pop, E. Thermal Dissipation and Variability in Electrical Breakdown of Carbon Nanotube Devices. *Phys. Rev. B* 2010, *82*, 205406.

- Hsieh, C.-T.; Citrin, D. S.; Ruden, P. P. Recombination-Mechanism Dependence of Transport and Light Emission of Ambipolar Long-Channel Carbon-Nanotube Field-Effect Transistors. *Appl. Phys. Lett.* **2007**, *90*, 012118.

- Guo, J.; Alam, M. A. Carrier Transport and Light-Spot Movement in Carbon-Nanotube Infrared Emitters. *Appl. Phys. Lett.* **2005**, *86*, 023105.

- Kane, E. O. Zener Tunneling in Semiconductors. J. Phys. Chem. Solids 1960, 12, 181–188.

- McGuire, D. L.; Pulfrey, D. L. A Multi-Scale Model for Mobile and Localized Electroluminescence in Carbon Nanotube Field-Effect Transistors. *Nanotechnology* **2006**, *17*, 5805– 5811.

- leong, M.; Solomon, P. M.; Laux, S. E.; Wong, H.-S. P.; Chidambarrao, D. Comparison of Raised and Schottky Source/Drain MOSFETs Using a Novel Tunneling Contact Model. *Tech. Dig. - Int. Electron Devices Meet.* **1998**, 733– 736.