Articles published week of 2 NOVEMBER 2009 Volume 95 Number 18

## Self-assembled nanodielectrics and silicon nanomembranes for low voltage, flexible transistors, and logic gates on plastic substrates

Hoon-Sik Kim,<sup>1</sup> Sang Min Won,<sup>2</sup> Young-Geun Ha,<sup>3</sup> Jong-Hyun Ahn,<sup>4</sup> Antonio Facchetti,<sup>3</sup> Tobin J. Marks,<sup>3</sup> and John A. Rogers<sup>1,2,a)</sup>

<sup>1</sup>Department of Materials Science and Engineering, University of Illinois, 1304 West Green Street, Urbana, Illinois 61801, USA

<sup>2</sup>Department of Electrical and Computer Engineering, University of Illinois, 1304 West Green Street, Urbana, Illinois 61801, USA

<sup>3</sup>Department of Chemistry and the Materials Research Center, Northwestern University, Evanston, Illinois 60208-3113, USA

<sup>4</sup>School of Advanced Materials Science and Engineering, SKKU Advanced Institute of Nanotechnology, Sungkyunkwan University, Suwon 440-746, Republic of Korea

(Received 20 August 2009; accepted 4 September 2009; published online 4 November 2009)

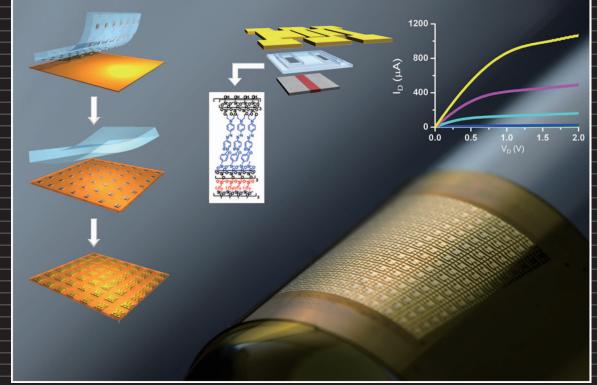

This letter reports the fabrication and electrical characterization of mechanically flexible and low operating voltage transistors and logic gates (NOT, NAND, and NOR gates) using printed silicon nanomembranes and self-assembled nanodielectrics on thin plastic substrates. The transistors exhibit effective linear mobilities of ~680 cm<sup>2</sup>/V s, on/off ratios >10<sup>7</sup>, gate leakage current densities  $<2.8 \times 10^{-7}$  A/cm<sup>2</sup>, and subthreshold slopes ~120 mV/decade. The inverters show voltage gains as high as 4.8. Simple digital logic gates (NAND and NOR gates) demonstrate the possible application of this materials combination in digital integrated circuits. © 2009 American Institute of Physics. [doi:10.1063/1.3256223]

With suitable design strategies, inorganic semiconductors can be used in mechanically compliant electronics for applications in areas, such as biomedical and bioinspired devices, lightweight/rugged electronics, and advanced communication and sensor systems, where conventional waferbased technologies cannot meet requirements.<sup>1–5</sup> We and others have demonstrated mechanically flexible and stretchable electronic devices such as metal-oxide-semiconductor thin-film transistors (MOS-TFTs) and various analog and digital integrated circuits (ICs) using single crystalline silicon micro/nanomembranes and ribbons (which we refer to as microstructured silicon,  $\mu$ s-Si) as building blocks.<sup>1,2,6</sup> A key element of these devices is the gate dielectric, due to its important role in determining the operating voltage and subthreshold characteristics. Although SiO<sub>2</sub> is a natural choice, temperature limitations associated with organic substrates frustrate the use of standard deposition procedures. Low temperature plasma-enhanced deposition provides a route to good, although not ideal properties.<sup>1</sup> As a result, besides the semiconductor itself, the material for the gate dielectric is the most challenging aspect of these systems. Recent research indicates that self-assembled nanodielectrics (SANDs), deposited at low temperatures, can serve as robust, low-leakage gate dielectrics in TFTs fabricated with a range of organic, nanotube,<sup>8</sup> and amorphous or polycrystalline inorganic thin-film semiconductors such as ZnO,<sup>9</sup>  $In_2O_3$ ,<sup>10</sup> and  $CdSe^{11}$  with exceptionally low leakage and excellent switching properties. This letter illustrates the utility of SANDs as gate dielectrics in  $\mu$ s-Si devices including n-channel MOS (NMOS) TFTs, inverters, and various logic gates on thin polyimide (PI) substrates.

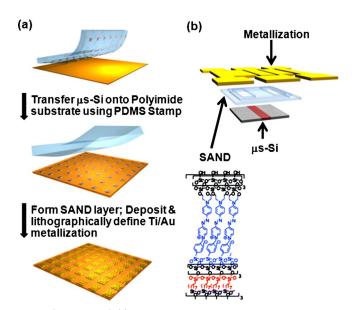

The fabrication begins by creating degenerately doped contact regions on p-type silicon-on-insulator wafers (150 mm SOITEC UNIBOUND; 300-nm-thick top silicon layer; resistivity=13.5–22.5  $\Omega$  cm, and 1000-nm-thick buried oxide layer) via phosphorous diffusion using a spin-on-dopant (P509; Filmtronics) and procedures described elsewhere.<sup>12</sup> Photolithography and reactive ion etching define the lateral dimensions of silicon nanomembranes (i.e., the form of the  $\mu$ s-Si) that are released from the wafer by etching the buried oxide with hydrofluoric acid, as illustrated in Fig. 1(a). As a source of  $\mu$ s-Si, bulk wafers can also be used.<sup>13</sup> Transfer printing next delivers these membranes onto a PI sheet (70- $\mu$ m-thick) coated with a thin, spin-cast layer of a liquid PI precursor (Sigma Aldrich) which serves as an adhesive.

FIG. 1. (Color online) (a) Schematic illustration of the fabrication process for  $\mu$ s-Si TFTs with SAND gate dielectrics. (b) Layout of the device, in an exploded layer-by-layer schematic view. The chemical structure of the SAND used here appears below.

## 95, 183504-1

## © 2009 American Institute of Physics

Downloaded 09 Nov 2009 to 130.126.101.208. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: jrogers@uiuc.edu.

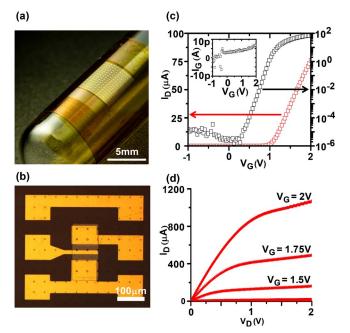

FIG. 2. (Color online) (a) Optical image of an array of  $\mu$ s-Si TFTs with SAND dielectrics on a PI (75- $\mu$ m-thick) substrate, wrapped around the test tube with diameter of 12 mm. (b) Optical images of an individual device. (c) Drain current (I<sub>D</sub>) as a function of gate voltage (V<sub>G</sub>) in both linear (gray) and logarithmic (black) scale, measured with source/drain bias (V<sub>D</sub>) of 50 mV. The inset shows the gate leakage current for V<sub>G</sub> between -1 and 2 V. (d) Drain current as a function of source/drain bias for various gate biases, for a typical device.

Self-assembled nanodielectrics (SANDs; ~15 nm thick) deposited<sup>9</sup> on the native oxide of the exposed membrane surfaces serve as gate dielectrics for the NMOS TFTs. The type of SAND used here consists of alternating organic layers (saturated alkyl and  $\pi$ -stilbazolium) strongly interconnected by glassy siloxane networks that planarize the surface and enhance structural integrity by cross-linking and filling pinholes. This SAND multilayer exhibits a capacitance of ~180 nF/cm<sup>2</sup>.<sup>9</sup> Etching defines openings in the SAND and native oxide for source and drain metallization. Photolithography and liftoff then define Ti/Au (10/150 nm) for source, gate, and drain electrodes, as well as for interconnects between transistors for logic gates.

Figure 2 provides optical images and electrical characterization data for representative NMOS TFTs. As shown in Fig. 2(b), the devices have channel lengths and widths of 7.5 and 100  $\mu$ m, respectively. Figure 2(c) presents a plot of the transfer characteristic in both linear (red) and logarithmic (black) scales where output (drain) current is plotted as a function of the input (gate) bias voltage for a fixed output (drain) voltage of 50 mV. The effective device mobility in the linear regime can be extracted from these data using a parallel plate capacitance model and standard analysis procedures.<sup>14</sup> The mobility for the device shown is  $\sim 680 \pm 50 \text{ cm}^2/\text{V}$  s, and the on/off ratio is  $> 10^7$ . Deviceto-device variation in the mobility is  $\sim 10\%$ , within the processing variation and measurement error typically observed. The leakage current to the gate through the SAND layer is <7 pA throughout the entire gate bias range (from -1 to 2 V) and is about 3.9 pA at 1 V, corresponding to leakage current densities of  $<2.8\times10^{-7}$  and  $\sim1.5\times10^{-7}$  A/cm<sup>2</sup>, respectively. These values are near the noise limit of our instrumentation; see inset of Fig. 2(c). The threshold voltage (V<sub>th</sub>) and subthreshold slope (S), also extracted from

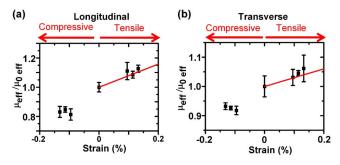

FIG. 3. (Color online) Normalized effective mobility as a function of bending-induced strain in the (a) longitudinal direction. (i.e., along the channel direction) (b) transverse direction (i.e., perpendicular to the channel direction). The gray lines correspond to independent measurements on wafer-based devices with similar dimensions.

transfer characteristics, are  $\sim 1.1 \pm 0.05$  V and the  $\sim$ 120 ± 4 mV/decade, respectively. The observed variations threshold voltage and the subthreshold slope in  $\sim 4\%$  and 3\%, respectively; both are within the measureare ment error that we typically observe. These performance parameters (effective device mobility, on/off ratio, and subthreshold slope) are all somewhat better than those previously reported on similar devices using a SiO<sub>2</sub> gate dielectric deposited at 250 °C by plasma-enhanced chemical vapor deposition (PECVD) (effective device mobility  $\approx 600 \text{ cm}^2/\text{V}$  s, on/off ratio  $\approx 10^5$ , and subthreshold slope  $\approx 230 \text{ mV/decade with 100 nm of SiO}_2$  dielectric layer).<sup>1</sup> More important than these differences is that SAND materials offer much more attractive processing conditions than PECVD SiO<sub>2</sub>. In particular, SANDs can be deposited near room temperature using solution processing, whereas PECVD SiO<sub>2</sub> requires higher temperatures and vacuum conditions. Figure 2(d) shows current-voltage data, indicating output resistances of 6.2, 13.4, 34.3, and 133.7 k  $\Omega$  at gate biases of 2, 1.75, 1.5, and 1.25 V, respectively.

To investigate the mechanical properties, we performed bending tests in the longitudinal (i.e., along the channel transport direction) and transverse (i.e., perpendicular to the longitudinal case) directions by measuring the electrical characteristics of the devices while wrapped on tubes having different circular cross-sections. This bending induces strain in the silicon, which can change the intrinsic mobility, as is well known.<sup>15</sup> Figure 3 shows the effective device mobility as a function of applied tensile and compressive strains in longitudinal and transversal directions, where the strain is computed from a mechanical analysis presented elsewhere.<sup>16</sup> The effective device mobilities were evaluated at calculated strains of 0.1%, 0.11%, and 0.13% which corresponds bend radii of 8.80, 7.35, and 6.35 mm, respectively. These variations are comparable to those observed by Zhao et al.,<sup>17</sup> where the effects of uniaxial tensile strain were studied on partially depleted SOI MOSFETs with device dimensions comparable to ours. These results appear as a solid line in Fig. 3. The effective device mobility increases under tensile strain and decreases under compressive strain.<sup>17,18</sup>

To demonstrate the applicability of SAND-based  $\mu$ s-Si transistors for circuit applications, we fabricated the three logic gates (NOT, NAND, and NOR gates) that are the essential building blocks of digital ICs. Other types of Boolean logic gates and higher level digital ICs (i.e., latches, flip flops, arithmetic logic unit, etc.) can be realized from a network of these logic gates. In all cases, we used NMOS for

Downloaded 09 Nov 2009 to 130.126.101.208. Redistribution subject to AIP license or copyright; see http://apl.aip.org/apl/copyright.jsp

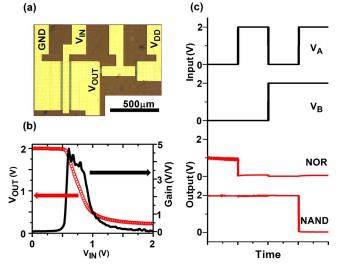

FIG. 4. (Color online) (a) Optical Image of an inverter based on  $\mu$ s-Si TFTs with SAND gate dielectrics. All logic gates (NOT, NAND, and NOR) are biased with V<sub>DD</sub>=2 V and GND (0 V). (b) VTC of an inverter (gray), and Gain (black). (c) Output characteristic of a NAND gate and a NOR gate. V<sub>A</sub> and V<sub>B</sub> represent the input voltages and V<sub>OUT</sub> represents the output voltage.

both pull-up and pull-down transistors, placing them in the category of enhancement-load NMOS logic.<sup>19</sup> Both the supply voltage  $(V_{DD})$  and the input voltage  $(V_{IN})$  were limited to 2 V, to demonstrate the possibility of low-voltage operation. Figure 4(a) shows an optical image of a representative inverter (NOT gate). The pull-down transistor has channel length and width of 15 and 500  $\mu$ m, respectively; the pull-up transistor has channel length and width of 400 and 50  $\mu$ m, respectively. The aspect ratios (Z) of the pull-up and pull-down are, then, 8.0 and 0.030, respectively. The geometric ratio (K<sub>R</sub>), defined as  $Z_{Pull-up}/Z_{Pull-down}$ , is ~266. From the voltage transfer curve (VTC) of the inverter shown in Fig. 4(b), several voltages are defined, namely V<sub>OH</sub>, V<sub>OL</sub>,  $V_{IL}$ ,  $V_{IH}$ ,  $V_M$ ,  $V_{MAX}$ , and  $V_{MIN}$ .  $V_{OH}$  and  $V_{OL}$ , by definition, represent the minimum output voltage for a valid "1," and the maximum output voltage for a valid "0," respectively. The device dimensions were selected based on design studies using PSPICE to make  $V_{\text{OL}}$  close to 0 V and  $V_{\text{OH}}$  close to 2 V.  $V_{IL}$  (voltage input low) and  $V_{IH}$  (voltage input high) are the input voltages at which the output voltage transfer curve has the slope of 1.0.  $V_M$  (voltage midpoint) is the voltage where the input and the output voltages are equal.  $V_{MAX}$ (maximum output voltage) and V<sub>MIN</sub> (minimum output voltage) are the maximum and minimum voltages that the output can reach. For the logic gate shown here, V<sub>OH</sub>, V<sub>OL</sub>, V<sub>IL</sub>,  $V_{\text{IH}}$ ,  $V_{\text{M}}$ ,  $V_{\text{MAX}}$ , and  $V_{\text{MIN}}$  are 1.95, 0.45, 0.54, 1.03, 0.84, 2, and 0.22 V, respectively. The resulting noise margins, NM<sub>L</sub> and NM<sub>H</sub>, thus become 0.09 and 0.92 V, respectively. NAND and NOR logic gates can be realized simply by adding a transistor to the input node of the inverter in series configuration for the NAND gate and in parallel configuration for the NOR gate. Figure 4(c) shows output characteristics of NAND and NOR gates, respectively.  $V_A$  and  $V_B$  are the input voltages. For the NAND gate, the output becomes "0" only when both inputs are "1." For the NOR gate, the output becomes "1" only when both inputs are "0." The logic "0" and "1" outputs of the NAND gate were 0.03 and 1.98 V to 2 V, respectively. The logic "0" and "1" outputs of the NOR gate were 0–0.07 and 0.98–1.07 V, respectively. Collectively, these results and those of the individual transistors demonstrate that the combination of single-crystalline silicon nanomembranes and SANDs provides an important route to mechanically flexible, high performance, and low-voltage digital ICs on plastic substrates.

We thank T. Banks for help in processing by use of facilities at the Frederick Seitz Materials Research Laboratory. The silicon and device components of the work were supported by a MURI award. The work on SANDs was supported at Northwestern University by ONR (Grant No. N00014-05-1-0766) and AFOSR (Grant No. FA9550-08-1-0331). Characterization facilities were provided by the Northwestern University MRSEC (NSF under Grant No. DMR-0520513).

- <sup>1</sup>J.-H. Ahn, H.-S. Kim, K. J. Lee, Z. Zhu, E. Menard, R. G. Nuzzo, and J. A. Rogers, IEEE Electron Device Lett. **27**, 460 (2006).

- <sup>2</sup>D.-H. Kim, J.-H. Ahn, W. M. Choi, H.-S. Kim, T.-H. Kim, J. Song, Y. Y. Huang, Z. J. Liu, C. Lu, and J. A. Rogers, Science **320**, 507 (2008).

- <sup>3</sup>J.-H. Ahn, H.-S. Kim, K. J. Lee, S. Jeon, S. J. Kang, Y. Sun, R. G. Nuzzo, and J. A. Rogers, Science **314**, 1754 (2006).

- <sup>4</sup>A. J. Baca, J.-H. Ahn, Y. Sun, M. A. Meitl, E. Menard, H.-S. Kim, W. M. Choi, D.-H. Kim, Y. Huang, and J. A. Rogers, Angew. Chem. Int. Ed. **47**, 5524 (2008).

- <sup>5</sup>Y. Sun and J. A. Rogers, Adv. Mater. **19**, 1897 (2007).

- <sup>6</sup>H.-C. Yuan and Z. Ma, Appl. Phys. Lett. 89, 212105 (2006).

- <sup>7</sup>S. DiBenedetto, A. Facchetti, M. A. Ratner, and T. J. Marks, Adv. Mater. **21**, 1407 (2009).

- <sup>8</sup>S.-H. Hur, M.-H. Yoon, A. Gaur, M. Shim, A. Facchetti, T. J. Marks, and J. A. Rogers, J. Am. Chem. Soc. **127**, 13808 (2005).

- <sup>9</sup>S. Ju, K. Lee, D. B. Janes, M.-H. Yoon, A. Facchetti, and T. J. Marks, Nano Lett. **5**, 2281 (2005).

- <sup>10</sup>H. S. Kim, P. D. Byrne, A. Facchetti, and T. J. Marks, J. Am. Chem. Soc. 130, 12580 (2008).

- <sup>11</sup>P. D. Byrne, A. Facchetti, and T. J. Marks, Adv. Mater. **20**, 2319 (2008).

- <sup>12</sup>Z.-T. Zhu, E. Menard, K. Hurley, R. G. Nuzzo, and J. A. Rogers, Appl. Phys. Lett. 86, 133507 (2005).

- <sup>13</sup>S. Mack, M. A. Meitl, A. J. Baca, Z.-T. Zhu, and J. A. Rogers, Appl. Phys. Lett. 88, 213101 (2006).

- <sup>14</sup>S. Sze, Semiconductor Devices: Physics and Technology (Wiley, New York, 1985), pp. 204–206.

- <sup>15</sup>C. S. Smith, Phys. Rev. **94**, 42 (1954).

- <sup>16</sup>S.-I. Park, J.-H. Ahn, X. Feng, S. Wang, Y. Huang, and J. A. Rogers, Adv. Funct. Mater. 18, 2673 (2008).

- <sup>17</sup>W. Zhao, J. He, R. E. Belford, L.-E. Wernersson, and A. Seabaugh, IEEE Trans. Electron Devices **51**, 317 (2004).

- <sup>18</sup>A. Hamada, T. Furusawa, N. Saito, and E. Takeda, IEEE Trans. Electron Devices **38**, 895 (1991).

- <sup>19</sup>J. Whitaker, *The Electronics Handbook* (CRC, Boca Raton, 1996), pp. 659–661.