## PROCESS AND MEASUREMENT BRIEFS

#### 3-D x-ray images

A microscope that uses direct-phase retrieval of coherent x-ray diffraction patterns with a novel tomographic reconstruction algorithm has been reported by lead investigator Subhash Risbud, Univ. of California, Davis. This method directs an x-ray source onto a gallium nitride (GaN) nanoparticle and collects the x-ray scattered from the sample. Then, computers construct a 3-D image from this data. The microscope resolves details down to 17 nm. The platelet structure of GaN and the formation of small islands on the surface of the platelets are observed, capturing the internal GaN-Ga<sub>2</sub>O<sub>3</sub> (gallium oxide) core shell structure. The work is described in the Nov. 24, 2006 issue of *Physical Review Letters*.

For information, contact Subhash Risbud at shrisbud@ucdavis.edu.

#### Leaves pure nanotubes

A two-step method (gas-phase plasma hydrocarbon reaction) that removes metallic single-walled carbon nanotubes (SWNTs) from a mixture of semiconducting and metallic nanotubes, leaving the remaining material with pure semiconducting electrical properties has been developed by lead investigator Hongjie Dai, Stanford Univ., Calif. In the process, methane plasma at 400°C is used to selectively etch metallic SWNTs in gas leaving only the semiconducting ones behind. These tubes are annealed under a vacuum at 600°C. Infrared (IR) microscopy shows that the processed nanotubes are clean and retain the electrical properties of non-etched semiconducting nanotubes. The work is described in the Nov. 10, 2006 issue of *Science*.

For information, contact Hongjie Dai at hdai@stanford.edu.

## **Targets measure relative positions**

Benchmark reference patterns, which check the precision and accuracy of overlay measurement equipment, have been improved by Richard Silver and colleagues, National Institute of Standards and Technology (NIST), Gaithersburg, Md. Target patterns are studied in which two sets of densely arranged nanoscale lines and grooves create a hybrid target that reflects light, creating an image measurable with a conventional optical microscope. The individual sets of lines are so dense that no individual optical image of the lines occurs, yet their combination results in an optical pattern. The intensity patterns of the reflected light are unique to the combination, and the patterns are easily analyzed to determine the relative position of the lines that make up the pattern—feature sizes range from 10- to 50-nm wide that are positioned 100-nm apart. The combined pattern magnifies by  ${>}40\times$  the size of the overlay offset between layers.

For information, contact Richard Silver at richard.silver@nist.gov.

## Simple method makes metal cups

A simple method that produces metal nanocups with a capacity measured in femtoliters has been reported by lead investigator G.U. Kulkarni, Jawaharlal Nehru Center for Advanced Scientific Research, Bangalore, India. These nanostructures are made from gold (Au), silver (Ag), copper (Cu), zinc (Zn), niobium (Nb), cadmium (Cd), aluminum (Al), indium (In), or tin (Sn) targets via laser ablation in a vacuum. The femto-cup formation is a result of a novel hydraulic jump generated by surface tension. And, as the inclination of the substrate is increased (away from the normal), the nanostructures become increasingly elliptical. Optimal pulse energy (~100 mJ/pulse) and substrate temperature that is slightly lower than the melting point of metal are key in producing the nanocups. And, at sizes <300-nm dia, nanocup formation is inhibited due to limited metal flow. The metal femto-cups can be transformed to form inert ceramic cups via external reactions. The work is described in the Nov. 16, 2006 issue of *Physical Chemistry B*.

For information, contact G.U. Kulkarni at kulkarni@jncasr.ac.in.

### Process and Measurement and Nanotechnology

# Integrate dissimilar materials onto one platform

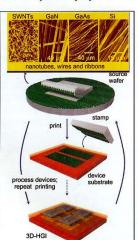

A simple method that combines dissimilar single-crystal inorganic semiconductors with one another and with other classes of nanomaterials to create heterogeneously integrated electronic systems with 2- or 3-D layouts has been demonstrated by lead investigator John Rogers at the Univ. of Illinois, Urbana-Champaign. The method enables incompati-

ble materials to be processed separately and then combined with others materials via a low-temperature process onto a variety of surfaces—flexible or rigid.

Generally, in the process (Fig. 1), nano- and microstructures, such as carbon nanotubes (CNTs) and single-crystal micro- and nanoscale wires and ribbons of gallium nitride (GaN), Si, and gallium arsenide (GaAs) are fabricated on individual substrates using conventional processes. Then, an elastomeric stamp-

Fig. 1. Steps for producing 2- or 3-D layouts. *Source:* Science.

based printing method is used to transfer these individual substrates to a device substrate such as polyimide (PI). The PI layer can be as thin as 500 nm, and on average, is 1- to 1.5-mm thick for the devices created. Then the stamp, which is covered with a spincast layer of a liquid pre-polymer (such as polyamic acid), is pressed onto a structure

and peeled away. Once the polymer cures, it adheres to the nanostructure when the stamp is lifted off, leaving the nanostructure behind. (Different nanostructured materials, such as CNTs, can be printed next to other ones on the same surface.)

Additional processing takes place, including deposition and patterning of gate dielectrics, electrodes, and interconnects. The transfer printing and device fabrication steps are repeated, beginning with spin-coating a new pre-polymer interlayer on top of a previously completed circuit level.

The method also makes multilayered systems. After the first layer of devices is printed, it is coated with a thin layer of polymer, which anchors the subsequent layer of devices as well as insulates between the layers. Since the polymer is thin, holes can be etched into it, allowing connections between devices in different layers.

The team fabricated a variety of devices, such as three-layer, 3-D stacks of arrays of Si MOSFETs (metal-oxide-semiconductor field-effect transistor).

Potential applications are electronics and optoelectronics.

The work is described in the Dec. 15, 2006 issue of *Science*.

Contact John Rogers at jrogers@uiuc.edu.

# Did you know . . .

Revenue from nanotechnologies in the food industry will grow to \$5.8 billion by 2012.

*—Cientifica*London