AFMDC6 ISSN 1616-301X Vol. 16, No. 18 December 4, 2006

ADANCED FUNCTIONA ALERAS

D53313

# Organic/Inorganic Gate Dielectrics for Flexible Electronics

Template-Based Preparation of PbTiO<sub>3</sub> Nanograins Platinum Binuclear Complexes as Dopants for OLEDs Efficient Synthesis of Carbon Nanotube/Nanoparticle Hybrids DOI: 10.1002/adfm.200600539

## Bilayer Organic–Inorganic Gate Dielectrics for High-Performance, Low-Voltage, Single-Walled Carbon Nanotube Thin-Film Transistors, Complementary Logic Gates, and p–n Diodes on Plastic Substrates\*\*

By Qing Cao, Ming-Gang Xia, Moonsub Shim, and John A. Rogers\*

High-capacitance bilayer dielectrics based on atomic-layer-deposited  $HfO_2$  and spin-cast epoxy are used with networks of single-walled carbon nanotubes (SWNTs) to enable low-voltage, hysteresis-free, and high-performance thin-film transistors (TFTs) on silicon and flexible plastic substrates. These  $HfO_2$ -epoxy dielectrics exhibit excellent properties including mechanical flexibility, large capacitance (up to ca. 330 nF cm<sup>-2</sup>), and low leakage current (ca.  $10^{-8}$  A cm<sup>-2</sup>); their low-temperature (ca.  $150 \,^{\circ}$ C) deposition makes them compatible with a range of plastic substrates. Analysis and measurements of these dielectrics as gate insulators in SWNT TFTs illustrate several attractive characteristics for this application. Their compatibility with polymers used for charge-transfer doping of SWNTs is also demonstrated through the fabrication of n-channel SWNT TFTs, low-voltage p-n diodes, and complementary logic gates.

### 1. Introduction

The possibility of using random networks<sup>[1-3]</sup> or aligned arrays of single-walled carbon nanotubes (SWNTs)<sup>[4-6]</sup> as semiconducting or conducting thin-film-type materials in the emerging field of flexible and large-area electronics<sup>[7]</sup> has recently attracted some attention. The unique electrical, mechanical, and thermal properties of SWNTs, as demonstrated pri-

marily through studies of single-tube devices such as transistors,<sup>[8]</sup> solar cells,<sup>[9]</sup> logic gates,<sup>[10]</sup> and ring oscillators,<sup>[11,12]</sup> make SWNTs a potentially attractive building block for thin-film devices. The absence of dangling bonds makes it possible for SWNTs to exhibit good electrical characteristics on a wide range of substrates, including plastics. This feature, combined with the ability to print the tubes at room temperature using dry transfer processes<sup>[13-15]</sup> or solution casting<sup>[16]</sup> make SWNT films potentially attractive for large-area and flexible electronics. Recent reports demonstrate that thin-film field-effect transistors (FETs) based on random networks of SWNTs can be successfully fabricated on plastic substrates, and that the resulting devices can achieve good electrical, mechanical, and even optical (e.g., transparency) properties.<sup>[13,17-</sup> <sup>20]</sup> Several major challenges must be overcome, however, in order to take full advantage of SWNT films for these applications. First, since as-grown carbon nanotubes are mixtures of metallic tubes and semiconducting tubes,<sup>[21,22]</sup> it is necessary to be able to grow semiconducting tubes only, perhaps by selective catalysis<sup>[23]</sup> or by plasma-enhanced chemical vapor deposition (CVD),<sup>[24]</sup> or to remove metallic tubes, perhaps by electrical breakdown<sup>[25,26]</sup> or chemical functionalization.<sup>[27–29]</sup> Several groups are working on these and related approaches, as they relate to applications of SWNTs in thin-film electronics as well as many other application areas. A second challenge, which is mainly related to active device applications, involves the development of materials for gate dielectrics that can be used to achieve high-performance n- and p-channel operation in SWNT TFTs, with low hysteresis, good mechanical properties, and compatibility for low-temperature plastic substrates.

The development of such gate dielectrics with high capacitance is crucial for applications of SWNT TFTs in low-power

<sup>[\*]</sup> Prof. J. A. Rogers Department of Chemistry, Materials Science and Engineering **Electrical and Computer Engineering** Mechanical and Industrial Engineering Beckman Institute and Frederick Seitz Materials Research Laboratory University of Illinois at Urbana-Champaign Urbana, IL 61801 (USA) E-mail: jrogers@uiuc.edu Q. Cao Department of Chemistry Beckman Institute and Frederick Seitz Materials Research Laboratory University of Illinois at Urbana-Champaign Urbana, IL 61801 (USA) M.-G. Xia Department of Materials Science and Engineering Beckman Institute and Frederick Seitz Materials Research Laboratory University of Illinois at Urbana-Champaign Urbana, IL 61801 (USA) Prof. M. Shim Department of Materials Science and Engineering University of Illinois at Urbana-Champaign Urbana, IL 61801 (USA) [\*\*] We thank T. Banks and D. Sievers for help with the processing. This

<sup>[\*\*]</sup> We thank I. Banks and D. Sievers for help with the processing. This work was supported by DARPA-funded AFRL-managed Macroelectronics Program Contract FA8650-04-C-7101, the U.S. Department of Energy under grant DEFG02-91-ER45439 and the NSF through grant NIRT-0403489.

flexible electronics. High capacitance also leads to high transconductance  $(g_m)$  and improved subthreshold slope (S), both of which are important for switching in digital circuits. Examples of single-tube, top-gate devices have been achieved with either ultrathin SiO<sub>2</sub><sup>[30]</sup> deposited using CVD or high  $\kappa$  dielectric materials such as zirconium oxide,<sup>[31]</sup> hafnium oxide,<sup>[32]</sup> and titanium oxide<sup>[33]</sup> deposited using atomic layer deposition (ALD). Polymer electrolytes have also been used, although the switching speeds that can be achieved are modest.<sup>[34-36]</sup> The top-gate design has the disadvantage that the deposition process can, in some cases, damage the tubes and that the top-gate structure makes it difficult to apply electrical breakdown procedures to remove metallic pathways or to perform chemical functionalization of the nanotubes. Self-assembled mono-[37] and multilayer<sup>[38]</sup> dielectrics have been successfully used as high-capacitance dielectrics for TFTs that use small-molecule or polymer semiconductors in a bottom-gate configuration.<sup>[39]</sup> This type of design was also recently implemented with SWNT networks to yield promising properties including low-voltage and hystersis-free operations.<sup>[40]</sup> These specialized materials have the disadvantage, however, that they must be

have the disadvantage, however, that they must be deposited in a multiple-step dipping sequence whose implementation in large-area, high-speed processes will require further development. Other work demonstrated with small-molecule and polymer TFTs seeks to avoid these limitations through the use of ultrathin crosslinked polymers,<sup>[41,42]</sup> anodized metals,<sup>[43–45]</sup> ALD inorganic films,<sup>[46]</sup> and other materials for high-capacitance dielectrics.

We report, in this article, a high-capacitance dielectric based on a bilayer of high  $\kappa$  HfO<sub>2</sub> film deposited using ALD and an ultrathin layer of crosslinked epoxy formed by spin-casting. The resulting films can be formed easily, over large areas, and on a range of substrates including low-temperature plastics. Their properties are studied independently and through measurements of bottom-gate SWNT TFTs formed by transfer printing SWNT networks onto layers of these dielectrics deposited on either Si wafers or plastic substrates. Additional experiments demonstrate the ability to use polymer functionalization to obtain n-type SWNT TFTs, p–n diodes, and CMOS-type (CMOS: complementary metal oxide semiconductor) inverters.

#### 2. Results and Discussion

#### 2.1. Device Structure and Dielectric Synthesis

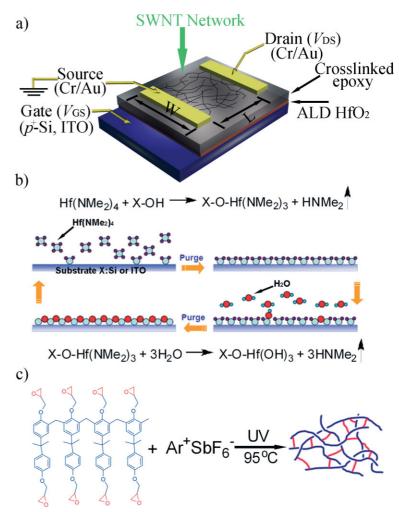

Figure 1a provides a schematic illustration of a bottom-gate SWNT TFT. Transfer-printing techniques that use poly(dimethylsiloxane) (PDMS; Sylgard 184, Dow Corning) stamps were used to form the devices, according to procedures described previously.<sup>[13]</sup> The behavior of SWNT TFTs can be described by the Shockley model for metal-insulatorsemiconductor (MIS) FETs, although their operation can also be influenced by Schottky barriers at the contacts.<sup>[47]</sup> The drain–source current ( $I_{\rm DS}$ ) can be modulated by a gate–source voltage ( $V_{\rm GS}$ ) applied across the gate dielectric and can be expressed by

$$I_{\rm DS} = \mu C_{\rm i} W \left[ (V_{\rm GS} - V_{\rm T} - 1/2 \ V_{\rm DS}) V_{\rm DS} \right] / L \tag{1}$$

in the linear region and

$$I_{\rm DS} = \mu C_{\rm i} W (V_{\rm GS} - V_{\rm T})^2 / 2L$$

<sup>(2)</sup>

in the saturation region, where  $\mu$  is the effective device mobility, W and L are the device channel width and channel length, respectively,  $V_{\rm T}$  is the threshold voltage, and  $C_{\rm i}$  is the capacitance of the gate dielectric. Increases in  $C_{\rm i}$  enable operation at reduced  $V_{\rm GS}$ , thereby decreasing the power consumption and increasing the switching speed and transconductance  $(g_{\rm m} = dI_{\rm DS}/dV_{\rm GS})$ .

To form high  $C_i$  gate dielectrics for this application we used conventional ALD methods to deposit, at temperatures of

**Figure 1.** a) Schematic illustration of a bottom-gate single-walled carbon nanotube network TFT with a high-capacitance  $HfO_2$ -epoxy bilayer gate dielectric.  $V_{GS}$ : gate-source voltage;  $V_{DS}$ : drain-source voltage; ITO: indium tin oxide. b) ALD reaction sequence. c) Chemistry of the epoxy component of the bilayer dielectric.

ca. 150 °C, ultrathin films of  $HfO_2$  on either Si wafer substrates or poly(ethyleneteraphtalate) (PET) films coated with indium tin oxide (ITO). The ALD cycle consists of a series of self-limiting surface reactions (Fig. 1b) to ensure the precise control of film thickness and to enable the formation of dense and pinhole-free films.<sup>[48]</sup> The approach can be applied to large areas with excellent reproducibility<sup>[49]</sup> and at low temperatures.<sup>[50]</sup> The crosslinked epoxy film that is implemented on top of the ALD layer is formed by spin-coating a precursor solution prepared using procedures described in the Experimental. The film thickness can be controlled by varying the concentration of precursors or the spinning speed. The precursors are polymerized by a cationic process initiated by the photogeneration of a Lewis acid (Fig. 1c). This epoxy film serves as an adhesion layer for high-yield transfer printing of the SWNT networks.

#### 2.2. Dielectrics Characterization

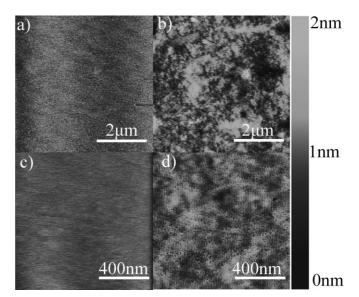

Good surface uniformity of the gate dielectric is crucial for reliably fabricating devices over large areas and for decreasing possible scattering of carriers due to surface roughness.<sup>[51-53]</sup> Figure 2 shows atomic force microscopy (AFM) images of ALD HfO<sub>2</sub> and HfO<sub>2</sub>–epoxy nanodielectrics on both Si wafer and PET substrates. For all cases the images indicate smooth (root-mean-square surface roughness 0.2–0.6 nm), defect-free films. The spin-cast epoxy layer increases this roughness slightly. The AFM images on ITO–PET were collected over 1  $\mu$ m × 1 $\mu$ m areas to minimize the influence of substrate non-planarity on the measurement.

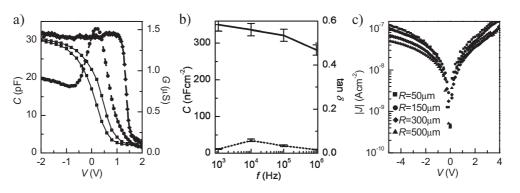

Leakage current and capacitance measurements provided direct information on the dielectric characteristics of the HfO<sub>2</sub>– epoxy bilayers. Capacitance–voltage (*C*–*V*) and conductance–voltage (*G*–*V*) measurements on MIS structures yielded both quasistatic and high-frequency ( $10^3$  to  $10^6$  Hz) behaviors (Fig. 3a). The measured response was typical of MIS devices for voltage sweeping from accumulation (negative bias with respect to the metal contact) to inversion (positive bias with respect to the metal contact) with a p<sup>+</sup>-Si wafer as the semiconductor substrate. The 0.2–0.4 V hysteresis in the high-frequency *C*–*V* curves and significant shift of the quasistatic *C*–*V* curves indicate that the HfO<sub>2</sub>–epoxy layers have certain quantities of fixed positive

charges and interface states. The fixed charges shift the flat-band voltage from the metal-semiconductor work-function difference; their density is estimated to be  $4 \times 10^{11}$  to  $8 \times 10^{11}$  cm<sup>-2</sup>.<sup>[54]</sup> Application of the Hill method<sup>[55]</sup> yielded the interface state density. *C*-*V* and *G*-*V* data evaluated at 100 KHz were used for this calculation so that no correction on the parasitic resistance was required on the measured value.<sup>[56]</sup> Thus, the interface state density is of the order of  $10^{12}$  eV<sup>-1</sup> cm<sup>-2</sup>, which is typical for high  $\kappa$  dielectrics ( $\kappa$ : dielectric constant).<sup>[57]</sup> Note here that this interface is between HfO<sub>2</sub> and Si, which is not directly relevant to the devices examined here. The interface trap density between the epoxy and SWNT is expected to be less due the absence of dangling bonds at the surface of the SWNTs.<sup>[58]</sup>

We measured the capacitances of a series of capacitors with different electrode areas. The capacitances were modeled as

$$C_{\text{total}} = PC_{\text{edge}} + AC_{\text{area}} \tag{3}$$

**Figure 2.** Tapping-mode AFM images of a) 5 nm HfO<sub>2</sub> on a p<sup>+</sup>-Si wafer, b) 5 nm HfO<sub>2</sub> and 10 nm crosslinked epoxy on a p<sup>+</sup>-Si wafer, c) 5 nm HfO<sub>2</sub> on ITO–PET, and d) 5 nm HfO<sub>2</sub> and 10 nm crosslinked epoxy on ITO–PET.

**Figure 3.** a) Quasistatic (dashed line) and high-frequency ( $10^5$  Hz) *C*–*V* (solid line) and *G*–*V* (dotted line) curves of a disk-shaped MIS capacitor with a diameter of 100µm. b) Frequency (*f*) dependence of the capacitances (solid line) and dissipation factors (dashed line) evaluated between  $10^3$  and  $10^6$  Hz. c) Leakage *J* versus voltage (*V*) for HfO<sub>2</sub>/crosslinked epoxy bilayer dielectrics measured on disk-shaped capacitors with different radii, *R*.

where  $C_{\text{total}}$  is the total capacitance of the given capacitor, *P* is the circumference of the round-shape metal pad,  $C_{\text{edge}}$  is the capacitance per unit length because of the edge effect, *A* is the area of the metal pad, and  $C_{\text{area}}$  is the capacitance per unit area.  $C_{\text{area}}$  is equal to  $336 \pm 15 \text{ nF cm}^{-2}$  at  $10^5$  Hz with slightly higher values at lower frequencies. This capacitance is much higher than that of dielectrics (e.g.,  $100 \text{ nm SiO}_2$ , ca.  $30 \text{ nF cm}^{-2}$ ) that are often used for SWNT TFTs; it is also twice as large as recently reported results for multilayered organic nanodielectrics

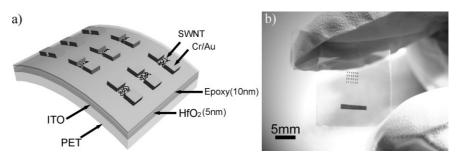

Figure 4. a) Schematic illustration and b) optical image of flexible, SWNT TFT devices that use  $HfO_2$ -epoxy bilayer dielectrics on an ITO-PET substrate.

(ca. 170 nF cm<sup>-2</sup>). The dissipation factors are in the range  $10^{-1}$  to  $10^{-2}$ , greater than those of thermal SiO<sub>2</sub>. Figure 3c depicts the leakage current density (*J*) versus voltage for MIS capacitors with different metal-pad sizes. These consistently low current densities suggest that leakage is not dominated by isolated sparse defects, and that the low leakage can be obtained reproducibly. The low defect density of HfO<sub>2</sub>–epoxy bilayer dielectrics is further corroborated by the high yield (>90 % for ca. 200 measured devices).

#### 2.3. Flexible SWNT TFTs Fabrication and Characterization

SWNT TFT arrays were fabricated on flexible ITO (ca. 100 nm)/PET (ca. 180  $\mu$ m) substrates with HfO<sub>2</sub>-epoxy nanodielectrics. Figure 4a shows a schematic illustration of these SWNT TFT arrays. A piece of PET film coated with ITO served as a flexible substrate and back gate. We thermally cycled the ITO/PET between 30 and 180 °C while it was laminated against a thin piece of PDMS chemically bonded to a glass slide (Corning Glass) to improve its dimensional stability during ALD processing.<sup>[59]</sup> Exposing the ITO/PET to ultraviolet induced ozone created a hydrophilic surface on which the  $HfO_2$  (5 nm) and epoxy (10 nm) layers were deposited. Transfer-printing techniques placed networks of SWNTs grown by CVD on SiO<sub>2</sub>/Si substrates directly onto the epoxy-HfO2-ITO-PET substrate stacks. This process used previously published approaches,<sup>[13]</sup> but with neutral gold etchants  $(KI + I_2)$  and basic chromium etchants  $(K_3Fe(CN)_6 + NaOH)$  to avoid etching of the ITO gate. Photolithography and liftoff defined source-drain electrodes of Cr/Au directly on top of the transfer-printed SWNT layer. Cutting strips (5  $\mu$ m wide spaced by 5  $\mu$ m, and oriented parallel to the direction of current flow in the channels) in the SWNT networks with oxygen plasma etching (Plasmatherm reactive-ion-etch system, 20 sccm  $O_2$  flow with a chamber base pressure of 100 mTorr (1 Torr = 133.322 Pa), 100 W RF power for 60 s) through a photopatterned layer of photoresist (Shipley 1805, Shipley, USA) electrically isolated individual TFTs and completed the fabrication process.<sup>[26]</sup> Figure 4b shows an optical image of the device arrays on the PET substrate.

Current–voltage (I-V) measurements were performed on devices fabricated with SWNT networks whose tube densities are much higher than the percolation threshold<sup>[60,61]</sup> (see Fig. 5a). Figure 5b shows the transfer curves of devices with different

channel lengths. The devices exhibit little hysteresis, which is in sharp contrast with devices built on thicker gate dielectrics and is similar to our previous devices utilizing ultrathin organic multilayers as the gate dielectric.<sup>[40]</sup> The threshold voltage ( $V_T$ ) is  $0.3\pm0.05$  V and does not vary substantially with channel length over this range. The on current ( $I_{ON}$ ) scales linearly with the reciprocal of the channel length, consistent with device operation that is not contact limited.  $I_{DS}-V_{DS}$  curves of these devices show current saturation when  $V_{DS} > V_{GS}-V_T$  (Fig. 5c), which is typical for well-designed transistors. Figure 5d shows

**Figure 5.** a) AFM image of part of a SWNT network in the channel region of a TFT device. b) Transfer curves of SWNT TFTs with an HfO<sub>2</sub>–epoxy dielectric, supported by a plastic substrate, and with channel lengths, from top to bottom, of 50  $\mu$ m, 75  $\mu$ m, and 100  $\mu$ m. The channel width in each case is 250  $\mu$ m. V<sub>DS</sub> is –0.2 V. Inset: *I*<sub>ON</sub> versus the reciprocal of channel length (1/*L*). c) *I*–V characteristics of a device with a channel length of 100  $\mu$ m and channel width of 250  $\mu$ m. The gate voltage varies between –1 and 1 V in steps of 0.5 V. d) Effective mobilities ( $\mu$ , solid line) calculated considering the effect of fringing field and on/off ratios (dash line) as a function of channel length for a typical set of devices.

linear region effective device mobilities, which are calculated considering the fringing field effect on the device gate capacitance,<sup>[18,62]</sup> and on/off ratios as a function of channel length. The detailed analysis and studies of the fringing field effect on capacitance coupling, which is important for the analysis of data obtained from these devices, and hysteresis will be reported elsewhere.<sup>[63]</sup> The mobilities, extracted while taking the effect of fringing field into consideration, are comparable to devices made on Si wafers with either HfO2-epoxy nanodielectrics or with thick (ca. 100 nm) thermal SiO<sub>2</sub> dielectrics (to the extent that they can be estimated reliably in the presence of large hysteresis). The channel length independent device mobilities are consistent with contact resistances that are negligible for the range of channel lengths studied here. The on/off ratio depends strongly on channel length because of the increasing probability of all metallic transport pathways with decreasing channel length. At long channel lengths, on/off ratios of ca. 10<sup>3</sup> can be achieved. Both the SWNT networks and HfO<sub>2</sub>-epoxy nanodielectrics are inert materials. We did not observe any change in device characteristics over several months of storage in ambient air.

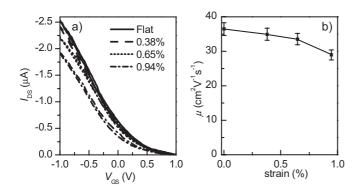

The mechanical robustness of the devices, which is limited mainly by the flexibility of HfO<sub>2</sub>–epoxy nanodielectrics, was examined through a series of bending tests with systems described previously.<sup>[64]</sup> Figure 6a shows the change of transfer curves of a typical device under tensile strain. Only small variations were observed for strains up to 1%. The small decrease of on current and device mobility (Fig. 6b) may be caused by the influence of strain on the contact between Au electrodes and SWNT films.<sup>[13]</sup> For strains larger than 1%, large leakage currents resulting from gate shorting were evident in most devices. Although the fracture strain of HfO<sub>2</sub>–epoxy nanodielectrics is inferior to most polymer dielectrics,<sup>[65]</sup> the degrees of bendability achieved here are sufficient for most applications in flexible electronics.

**Figure 6.** a) Transfer curves of a device with channel length of 75  $\mu$ m and channel width of 250  $\mu$ m at various levels of bending-induced tensile strains. V<sub>DS</sub> is fixed at –0.2 V. b) Variation of device mobility ( $\mu$ ) with tensile strain.

#### 2.4. Subthreshold Behavior of SWNT TFTs Based on HfO<sub>2</sub>-Epoxy Nanodielectrics

For many circuit applications, the subthreshold slope (S) is an important characteristic because it determines the change in gate voltage needed to turn the device off and on. Low-power circuits demand small S and  $V_{\rm T}$ . The value of the S is determined by the gate capacitance and the capacitance resulting from interface traps,  $C_{\rm IT}$ , according to

$$S = (k_{\rm B}T/e)\ln(10)(1 + C_{\rm IT}/C_{\rm i})^{[66]}$$

(4)

The room-temperature limit, 60 mV dec<sup>-1</sup>, can be accomplished in single-tubed devices with either electrolyte gating<sup>[34]</sup> or 2-3 nm ALD HfO<sub>2</sub> dielectrics deposited conformally on DNA-functionalized SWNTs.[67] However, in network devices, only relatively large S values ( $800-2500 \text{ mV dec}^{-1}$ ) have been reported. With HfO<sub>2</sub>-epoxy dielectrics, S as small as 280 mV dec<sup>-1</sup>was achieved in devices with 100 µm channel lengths (Fig. 7a). This low value results partly from a small  $C_{\rm IT}/C_{\rm i}$ , because of a large  $C_{\rm i}$ . This value represents substantial progress over devices fabricated with lower capacitance dielectrics, but it is still much higher than the theoretical limit. There are three possible reasons for this nonideal value. First,  $C_{\rm IT}$ could be much larger than  $C_i$  even for devices based on highcapacitance nanodielectrics. To test this argument, we fabricated a set of devices using only the HfO<sub>2</sub> layer (5 nm) as the gate dielectric, by using a kinetically controlled transfer-printing technique.<sup>[68]</sup> Such devices exhibit, however, only a marginal improvement of S, that is, from 280 to  $260 \text{ mV dec}^{-1}$ (Fig. 7b), despite the significant increase of  $C_i$ . This result suggests that the interface traps between the SWNT film and gate

**Figure 7.** Transfer characteristics plotted for devices that use a) 5 nm HfO<sub>2</sub> and 10 nm crosslinked epoxy or b) 5 nm HfO<sub>2</sub> as the gate dielectric. In both cases, the channel width and length are 250 and 100  $\mu$ m, respectively. V<sub>DS</sub> is –0.2 V. The dotted lines indicate the slope used to determine S. c) Transfer characteristics of devices with different channel lengths. The channel lengths are, from top to bottom, 5, 10, 30, 50, 75, and 100  $\mu$ m. The channel widths are 250  $\mu$ m. The V<sub>DS</sub> is –0.2 V. d) S versus device on/ off ratios.

dielectrics are not the major reason for the higher than expected S values. (The lower current levels of devices with only the HfO<sub>2</sub> layer as the dielectric results from the poor transferprinting efficiency in this case.) A second possibility is that the relatively low on/off ratios degrade the subthreshold performance because conduction through the metallic tubes does not change with  $V_{GS}$ . A channel-length scaling analysis of S, which shows that S decreases rapidly with increasing on/off ratio, suggests that conduction through metallic network pathways is the most important reason for nonideal performances (Fig. 7c and d). This effect is not explicitly included in Equation 4, which applies to devices with high on/off ratios. The third possibility is that the cylindrical shape of the SWNTs makes the bottomgate structure inferior to top-gate structures in terms of electrostatic coupling between  $V_{GS}$  and the channel, which may account, together with the capacitance difference, for the larger S with our HfO<sub>2</sub>-epoxy nanodielectrics than that obtained from polymer-electrolyte gatings at similar on/off ratios.<sup>[36]</sup>

#### 2.5. n-Type Devices and Complimentary Logic Gates

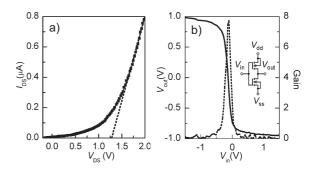

Controlling charge-carrier type is crucial for electronic circuit design. Pristine nanotubes typically lead to p-channel operation in transistors, when high-work-function metals are used for the source and drain. Single-tube devices with n-channel operation can be achieved by charge-transfer doping with alkaline metals<sup>[69,70]</sup> or amine-containing molecules,<sup>[71-73]</sup> by surface passivation,<sup>[74]</sup> by use of low-work-function metal contacts<sup>[75]</sup> or by nitrogen-atom doping.<sup>[76]</sup> Here, we demonstrate the compatibility of the HfO<sub>2</sub>-epoxy dielectrics with charge-transfer induced polarity switching with polyethyleneimine (PEI) coatings<sup>[77]</sup> using procedures described previously.<sup>[26]</sup> In n-channel mode, the devices exhibit very low hysteresis (Fig. 8a) with good scaling properties with channel lengths, similar to observations on p-channel devices. The average device mobility extracted from linear region considering the fringing field effect was at  $13\pm2$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. Sweeping the gate voltage from negative to positive leads to a negative shift of threshold voltage in the reverse scan, which indicates that holes are trapped at the dielectrics in these n-type de-

#### 1.5 F b) a) 1.0 /<sub>DS</sub>(μA) (Au) 0.5 0.0 1.0 V<sub>DS</sub>(V) -1.0 -0.5 0.0 0.5 1.0 0.0 0.5 1.5 2.0 $V_{GS}(V)$

**Figure 8.** a) Transfer curves of SWNT TFTs that use HfO<sub>2</sub>-epoxy dielectrics with channel lengths, from top to bottom, of 50, 75, and 100  $\mu$ m after uniformly coating the channel regions with PEI. The channel widths are 250  $\mu$ m.  $V_{DS}$  is 0.2 V. b) *I*-V characteristics of a device with a channel length and width of 100 and 250  $\mu$ m, respectively. The gate voltage varies between -1 and 1 V in steps of 0.5 V.

vices. This behavior is opposite to the electron trapping observed in p-type devices and indicates that surface traps mainly affect the more abundant carrier type. Figure 8b shows  $I_{DS}-V_{DS}$  characteristics of a typical n-channel device.

As a consequence of the compatibility of the HfO<sub>2</sub>-epoxy dielectrics with both p- and n-channel SWNT TFTs, the fabrication of p-n diodes and complementary logic devices is possible. Such diodes are important in microelectronics and nanotubebased p-n diodes have been demonstrated by means of chemical doping<sup>[78]</sup> and electrostatic doping.<sup>[79,80]</sup> The p-n diodes here were fabricated by covering half of the channel of the SWNT TFTs with PEI. Transport measurements clearly show current rectification and low turn-on voltage (Fig. 9a). A complementary type inverter was fabricated by integrating a pchannel and an n-channel SWNT TFT. These two devices were biased in the configuration depicted in the inset of Figure 9b. The high transconductances and on/off ratios enable gains (ca. 8) that are much better than those achieved with thick dielectrics;<sup>[81-84]</sup> they are comparable to SWNT network CMOS inverters fabricated with organic multilayer nanodielectrics<sup>[40]</sup> and single-tube inverters based on local bottom-gated devices.<sup>[11]</sup>

**Figure 9.** a) Transfer characteristics of a p–n diode ( $L=100 \mu m$ ,  $W=200 \mu m$ ). The dotted line shows the turn-on voltage of this diode. The p–n diode is formed by patterning PEI onto one half of the channel region, such that one half of the channel is p-type and the other half is n-type. b)  $V_{out}$  versus  $V_{in}$  curve for an inverter formed with p- and n-type SWNT TFTs based on HfO<sub>2</sub>–epoxy dielectrics. The inset shows the circuit diagram of this inverter.

#### 3. Conclusions

This paper demonstrates that a bilayer stack of HfO<sub>2</sub> and epoxy affords a robust, smooth, pinhole free, high capacitance, and low-leakage gate dielectric for SWNT TFTs that can be fabricated easily on both Si wafers and plastics by use of transfer-printing methods. The experimental results illuminate properties of these dielectrics and their behavior in TFTs. Transistors based on SWNT networks, including hysteresis-free p- and n-type SWNT TFTs with small subthreshold slope, p–n diodes, and high-gain complementary logic gates that operate at low voltages were realized. The results indicate that this type of dielectric can be useful in the development of nanotube-based thin-film-type electronic systems.

#### 4. Experimental

*Reagents*: HfO<sub>2</sub> ALD films were grown using H<sub>2</sub>O and Hf(NMe<sub>2</sub>)<sub>4</sub> (Me: methyl, Aldrich, 99.99 + %). The carrier gas in the ALD reactor was N<sub>2</sub> (Matheson Tri-Gas, 99.9995 %). Photocurable epoxy solutions were prepared by diluting commercially available precursors (SU-8 2, Microchem) with cyclopentanone (SU-8 2000 thinner, Microchem) at different volumetric ratios. The gold etchant was prepared by mixing 5% I<sub>2</sub> (Sigma–Aldrich, 99.99%), 10% KI (Sigma, 99.0%) and 85% dionized water. The chromium etchant was prepared by dissolving a small amount of NaOH (Sigma–Aldrich, 85.0%) in saturated K<sub>3</sub>Fe(CN)<sub>6</sub> (Sigma–Aldrich, 99.99%) aqueous solution.

*Materials*: p<sup>+</sup>-Si wafers (Montco Silicon Tech) and ITO-coated PET films ( $\leq 10 \Omega$ /sq, Delta Technologies) were cleaned according to standard procedures [85] and exposed to UV ozone for 3 min before ALD deposition to remove possible fluorine contamination [86] and to render the surface hydrophilic.

*Film Fabrication:* SWNT networks were synthesized as previously described [20]. The ALD HfO<sub>2</sub> film was deposited with a commercial ALD reactor (Savannah 100, Cambridge Nanotech.). One ALD reaction cycle consisted of one dose of water followed by a 2 s exposure and 5 s purge and then one dose of Hf(NMe<sub>2</sub>)<sub>4</sub> followed by another 2 s exposure and 5 s purge. During deposition, the nitrogen flow was fixed at 20 sccm and the chamber temperature was set at 150 °C. The deposition rate for hafnium oxide was 0.093 nm per cycle. For crosslinked epoxy film fabrication, the precursor solution was spin-coated at 4000 rpm, baked at 65 °C and 95 °C for 1 min each, exposed with an i-line (365 nm) UV lamp at an intensity of 15.0 mV cm<sup>-2</sup> for 12 s, and then cured at 95 and 120 °C for 1 min to afford a 10±1 nm thick film.

*Film Characterization*: The thicknesses of the hafnium oxide ALD films, the tube density of SWNT networks, and the surface morphologies of all thin films were evaluated using AFM (Dimension 3100 atomic force microscope, Digital Instruments) in tapping mode. The thicknesses of the epoxy films were measured using a profilometer (Dektak 3030).

*Electrical Measurement:* SWNT TFT measurements were carried out in air using a semiconductor parameter analyzer (Agilent 4155C), operated using an Agilent Metrics I/CV Lite program and GBIP communication. Triaxial and coaxial shielding was incorporated into a Signatone probe station to achieve better signal/noise ratio. Agilent 4282A precision LCR (inductance, capacitance, and resistance) meter was used for capacitance and impedance measurements.

> Received: June 20, 2006 Revised: August 1, 2006

Published online: November 7, 2006

- [1] E. S. Snow, J. P. Novak, M. D. Lay, E. H. Houser, F. K. Perkins, P. M. Campbell, *J. Vac. Sci. Technol. B* **2004**, *22*, 1990.

- [2] Z. Wu, Z. Chen, X. Du, J. M. Logan, J. Sippel, M. Nikolou, K. Kamaras, J. R. Reynolds, D. B. Tanner, A. F. Hebard, A. G. Rinzler, *Science* 2004, 305, 1273.

- [3] M. Kaempgen, G. S. Duesberg, S. Roth, Appl. Surf. Sci. 2005, 252, 425.

- [4] S. Han, X. L. Liu, C. W. Zhou, J. Am. Chem. Soc. 2005, 127, 5294.

- [5] A. Ismach, L. Segev, E. Wachtel, E. Joselevich, *Angew. Chem. Int. Ed.* 2004, 43, 6140.

- [6] C. Kocabas, M. Shim, J. A. Rogers, J. Am. Chem. Soc. 2006, 128, 4540.

- [7] R. H. Reuss, B. R. Chalamala, A. Moussessian, M. G. Kane, A. Kumar, D. C. Zhang, J. A. Rogers, M. Hatalis, D. Temple, G. Moddel, B. J. Eliasson, M. J. Estes, J. Kunze, E. S. Handy, E. S. Harmon, D. B. Salzman, J. M. Woodall, M. A. Alam, J. Y. Murthy, S. C. Jacobsen, M. Olivier, D. Markus, P. M. Campbell, E. Snow, *Proc. IEEE* 2005, 93, 1239.

- [8] S. J. Tans, A. R. M. Verschueren, C. Dekker, Nature 1998, 393, 49.

- [9] J. U. Lee, Appl. Phys. Lett. 2005, 87, 073 101.

- [10] A. Bachtold, P. Hadley, T. Nakanishi, C. Dekker, *Science* 2001, 294, 1317.

- [11] A. Javey, Q. Wang, A. Ural, Y. M. Li, H. J. Dai, Nano Lett. 2002, 2, 929.

- [12] Z. H. Chen, J. Appenzeller, Y. M. Lin, J. Sippel-Oakley, A. G. Rinzler, J. Y. Tang, S. J. Wind, P. M. Solomon, P. Avouris, *Science* 2006, *311*, 1735.

- [13] S.-H. Hur, O. O. Park, J. A. Rogers, Appl. Phys. Lett. 2005, 86, 243 502.

- [14] Y. X. Zhou, L. B. Hu, G. Grüner, Appl. Phys. Lett. 2006, 88, 123109.

- [15] X. L. Liu, S. Han, C. W. Zhou, Nano Lett. 2006, 6, 34.

- [16] M. A. Meitl, Y. X. Zhou, A. Gaur, S. Jeon, M. L. Usrey, M. S. Strano, J. A. Rogers, *Nano Lett.* 2004, *4*, 1643.

- [17] K. Bradley, J. C. P. Gabriel, G. Grüner, Nano Lett. 2003, 3, 1353.

- [18] E. S. Snow, P. M. Campbell, M. G. Ancona, J. P. Novak, *Appl. Phys. Lett.* 2005, 86, 033 105.

- [19] E. Artukovic, M. Kaempgen, D. Hecht, S. Roth, G. Grüner, *Nano Lett.* 2005, 5, 757.

- [20] Q. Cao, S.-H. Hur, Z.-T. Zhu, Y. Sun, C. Wang, M. Meitl, M. Shim, J. A. Rogers, Adv. Mater. 2006, 18, 304.

- [21] P. Avouris, Acc. Chem. Res. 2002, 35, 1026.

- [22] M. Ouyang, J.-L. Huang, C. M. Lieber, Acc. Chem. Res. 2002, 35, 1018.

- [23] S. M. Bachilo, L. Balzano, J. E. Herrera, F. Pompeo, D. E. Resasco, R. B. Weisman, *J. Am. Chem. Soc.* 2003, *125*, 11 186.

- [24] Y. Li, D. Mann, M. Rolandi, W. Kim, A. Ural, S. Hung, A. Javey, J. Cao, D. Wang, E. Yenilmez, Q. Wang, J. F. Gibbons, Y. Nishi, H. Dai, *Nano Lett.* 2004, 4, 317.

- [25] P. G. Collins, M. S. Arnold, P. Avouris, Science 2001, 292, 706.

- [26] Y. Zhou, A. Gaur, S.-H. Hur, C. Kocabas, M. A. Meitl, M. Shim, J. A. Rogers, *Nano Lett.* 2004, *4*, 2031.

- [27] M. S. Strano, C. A. Dyke, M. L. Usrey, P. W. Barone, M. J. Allen, H. Shan, C. Kittrell, R. H. Hauge, J. M. Tour, R. E. Smalley, *Science* 2003, 301, 1519.

- [28] L. An, Q. Fu, C. Lu, J. Liu, J. Am. Chem. Soc. 2004, 126, 10520.

- [29] C. Wang, Q. Cao, T. Ozel, A. Gaur, J. A. Rogers, M. Shim, J. Am. Chem. Soc. 2005, 127, 11460.

- [30] S. J. Wind, J. Appenzeller, R. Martel, V. Derycke, P. Avouris, *Appl. Phys. Lett.* 2002, *81*, 1359.

- [31] A. Javey, H. Kim, M. Brink, Q. Wang, A. Ural, J. Guo, P. McIntyre, P. McEuen, M. Lundstrom, H. J. Dai, *Nat. Mater.* 2002, 1, 241.

- [32] A. Javey, J. Guo, D. B. Farmer, Q. Wang, D. W. Wang, R. G. Gordon, M. Lundstrom, H. J. Dai, *Nano Lett.* **2004**, *4*, 447.

- [33] M. H. Yang, K. B. K. Teo, L. Gangloff, W. I. Milne, D. G. Hasko, Y. Robert, P. Legagneux, *Appl. Phys. Lett.* **2006**, 88, 113 507.

- [34] S. Rosenblatt, Y. Yaish, J. Park, J. Gore, V. Sazonova, P. L. McEuen, *Nano Lett.* 2002, 2, 869.

- [35] C. G. Lu, Q. Fu, S. M. Huang, J. Liu, Nano Lett. 2004, 4, 623.

- [36] T. Ozel, A. Gaur, J. A. Rogers, M. Shim, Nano Lett. 2005, 5, 905.

- [37] M. Halik, H. Klauk, U. Zschieschang, G. Schmid, C. Dehm, M. Schutz, S. Maisch, F. Effenberger, M. Brunnbauer, F. Stellacci, *Nature* 2004, 431, 963.

- [38] M. H. Yoon, A. Facchetti, T. J. Marks, Proc. Natl. Acad. Sci. USA 2005, 102, 4678.

- [39] A. Facchetti, M. H. Yoon, T. J. Marks, Adv. Mater. 2005, 17, 1705.

- [40] S. H. Hur, M. H. Yoon, A. Gaur, M. Shim, A. Facchetti, T. J. Marks, J. A. Rogers, J. Am. Chem. Soc. 2005, 127, 13808.

- [41] L. L. Chua, P. K. H. Ho, H. Sirringhaus, R. H. Friend, Appl. Phys. Lett. 2004, 84, 3400.

- [42] M. H. Yoon, H. Yan, A. Facchetti, T. J. Marks, J. Am. Chem. Soc. 2005, 127, 10 388.

- [43] J. Tate, J. A. Rogers, C. D. W. Jones, B. Vyas, D. W. Murphy, W. J. Li, Z. A. Bao, R. E. Slusher, A. Dodabalapur, H. E. Katz, *Langmuir* 2000, 16, 6054.

- [44] L. A. Majewski, R. Schroeder, M. Grell, Adv. Funct. Mater. 2005, 15, 1017.

- [45] L. A. Majewski, R. Schroeder, M. Grell, P. A. Glarvey, M. L. Turner, J. Appl. Phys. 2004, 96, 5781.

- [46] H. J. Kim, S. J. Kang, D. S. Park, K. B. Chung, M. Noh, C. N. Whang, M. H. Cho, *J. Korean Phys. Soc.* 2004, 45, 935.

- [48] L. Niinisto, J. Paivasaari, J. Niinisto, M. Putkonen, M. Nieminen, *Phys. Status Solidi A* 2004, 201, 1443.

- [49] M. Leskela, M. Ritala, Angew. Chem. Int. Ed. 2003, 42, 5548.

- [50] M. J. Biercuk, D. J. Monsma, C. M. Marcus, J. S. Becker, R. G. Gordon, *Appl. Phys. Lett.* **2003**, 83, 2405.

- [51] S. Takagi, A. Toriumi, M. Iwase, H. Tango, *IEEE Trans. Electron Devices* 1994, 41, 2357.

- [52] D. Knipp, R. A. Street, A. R. Volkel, Appl. Phys. Lett. 2003, 82, 3907.

- [53] S. E. Fritz, T. W. Kelley, C. D. Frisbie, J. Phys. Chem. B 2005, 109, 10574.

- [54] R. S. Muller, T. I. Kamins, M. S. Chan, Device Electronics for Integrated Circuits, Wiley, New York 2003.

- [55] W. A. Hill, C. C. Coleman, Solid-State Electron. 1980, 23, 987.

- [56] E. K. Evangelou, C. Wiemer, M. Fanciulli, M. Sethu, W. Cranton, J. Appl. Phys. 2003, 94, 318.

- [57] J. Robertson, Eur. Phys. J.: Appl. Phys. 2004, 28, 265.

- [58] A. Javey, J. Guo, D. B. Farmer, Q. Wang, E. Yenilmez, R. G. Gordon, M. Lundstrom, H. J. Dai, *Nano Lett.* 2004, *4*, 1319.

- [59] L. S. Zhou, S. Y. Jung, E. Brandon, T. N. Jackson, *IEEE Trans. Electron Devices* 2006, 53, 380.

- [60] L. Hu, D. S. Hecht, G. Grüner, Nano Lett. 2004, 4, 2513.

- [61] S. Kumar, J. Y. Murthy, M. A. Alam, Phys. Rev. Lett. 2005, 95, 066 802.

- [62] J. Guo, S. Goasguen, M. Lundstrom, S. Datta, Appl. Phys. Lett. 2002, 81, 1486.

- [63] Q. Cao, M. G. Xia, C. Kocabas, M. Shim, S. V. Rotkin, J. A. Rogers, unpublished.

- [64] E. Menard, R. G. Nuzzo, J. A. Rogers, Appl. Phys. Lett. 2005, 86, 093 507.

- [65] J.-A. Schweitz, MRS Bull. 1992, 17, 34.

- [66] S. Kumar, N. Pimparkar, J. Y. Murthy, M. A. Alam, *Appl. Phys. Lett.* 2006, 88, 123 505.

- [67] Y. R. Lu, S. Bangsaruntip, X. R. Wang, L. Zhang, Y. Nishi, H. J. Dai, J. Am. Chem. Soc. 2006, 128, 3518.

- [68] M. A. Meitl, Z. T. Zhu, V. Kumar, K. J. Lee, X. Feng, Y. Y. Huang, I. Adesida, R. G. Nuzzo, J. A. Rogers, *Nat. Mater.* **2006**, *5*, 33.

- [69] J. Kong, C. W. Zhou, E. Yenilmez, H. J. Dai, Appl. Phys. Lett. 2000, 77, 3977.

- [70] A. Javey, R. Tu, D. B. Farmer, J. Guo, R. G. Gordon, H. J. Dai, *Nano Lett.* 2005, 5, 345.

- [71] M. Shim, A. Javey, N. W. S. Kam, H. J. Dai, J. Am. Chem. Soc. 2001, 123, 11 512.

- [72] C. Klinke, J. Chen, A. Afzali, P. Avouris, Nano Lett. 2005, 5, 555.

- [73] G. P. Siddons, D. Merchin, J. H. Back, J. K. Jeong, M. Shim, Nano Lett. 2004, 4, 927.

- [74] D. Kaminishi, H. Ozaki, Y. Ohno, K. Maehashi, K. Inoue, K. Matsumoto, Y. Seri, A. Masuda, H. Matsumura, *Appl. Phys. Lett.* 2005, *86*, 113115.

- [75] Y. Nosho, Y. Ohno, S. Kishimoto, T. Mizutani, Appl. Phys. Lett. 2005, 86, 073 105.

- [76] K. Xiao, Y. Q. Liu, P. A. Hu, G. Yu, Y. M. Sun, D. B. Zhu, J. Am. Chem. Soc. 2005, 127, 8614.

- [77] M. Shim, T. Ozel, A. Gaur, C. Wang, J. Am. Chem. Soc. 2006, 128, 7522.

- [78] C. W. Zhou, J. Kong, E. Yenilmez, H. J. Dai, Science 2000, 290, 1552.

- [79] M. Freitag, M. Radosavljevic, Y. X. Zhou, A. T. Johnson, W. F. Smith, *Appl. Phys. Lett.* **2001**, *79*, 3326.

- [80] J. U. Lee, P. P. Gipp, C. M. Heller, Appl. Phys. Lett. 2004, 85, 145.

- [81] S.-H. Hur, C. Kocabas, A. Gaur, M. Shim, O. O. Park, J. A. Rogers, J. Appl. Phys. 2005, 98, 114302.

- [82] V. Derycke, R. Martel, J. Appenzeller, P. Avouris, *Nano Lett.* 2001, 1, 453.

- [83] X. L. Liu, C. Lee, C. W. Zhou, J. Han, Appl. Phys. Lett. 2001, 79, 3329.

- [84] P. Avouris, J. Appenzeller, R. Martel, S. J. Wind, Proc. IEEE 2003, 91, 1772.

- [85] G. E. Anner, *Planar Processing Primer*, Van Nostrand Reinhold, New York 1990.

- [86] D. M. Hausmann, E. Kim, J. Becker, R. G. Gordon, *Chem. Mater.* 2002, 14, 4350.